US 20080296565A1

(19) **United States**

(12) **Patent Application Publication**

**PARK et al.**

(10) **Pub. No.: US 2008/0296565 A1**

(43) **Pub. Date: Dec. 4, 2008**

(54) **METHOD OF FABRICATING POLYCRYSTALLINE SILICON LAYER, TFT FABRICATED USING THE SAME, METHOD OF FABRICATING TFT, AND ORGANIC LIGHT EMITTING DIODE DISPLAY DEVICE HAVING THE SAME**

(75) Inventors: **Byoung-Keon PARK, Suwon-si (KR); Jin-Wook SEO, Suwon-si (KR); Tae-Hoon YANG, Suwon-si (KR); Kil-Won LEE, Suwon-si (KR); Ki-Yong LEE, Suwon-si (KR)**

Correspondence Address:

**STEIN, MCEWEN & BUI, LLP

1400 EYE STREET, NW, SUITE 300

WASHINGTON, DC 20005 (US)**

(73) Assignee: **Samsung SDI Co., Ltd., Suwon-si (KR)**

(21) Appl. No.: **12/130,340**

(22) Filed: **May 30, 2008**

(30) **Foreign Application Priority Data**

May 31, 2007 (KR) ..... 2007-53314

**Publication Classification**

(51) **Int. Cl.**

**H01L 51/52** (2006.01)

**H01L 21/322** (2006.01)

**H01L 29/786** (2006.01)

**H01L 21/336** (2006.01)

(52) **U.S. Cl. .... 257/40; 438/471; 257/66; 438/166; 257/E29.273; 257/E21.317; 257/E21.412; 257/E51.018**

(57) **ABSTRACT**

A method of fabricating a polycrystalline silicon layer includes: forming an amorphous silicon layer on a substrate; crystallizing the amorphous silicon layer into a polycrystalline silicon layer using a crystallization-inducing metal; forming a metal layer pattern or metal silicide layer pattern in contact with an upper or lower region of the polycrystalline silicon layer corresponding to a region excluding a channel region in the polycrystalline silicon layer; and annealing the substrate to getter the crystallization-inducing metal existing in the channel region of the polycrystalline silicon layer to the region in the polycrystalline silicon layer having the metal layer pattern or metal silicide layer pattern. Accordingly, the crystallization-inducing metal existing in the channel region of the polycrystalline silicon layer can be effectively removed, and thus a thin film transistor having an improved leakage current characteristic and an OLED display device including the same can be fabricated.

FIG. 1A

FIG. 1B

FIG. 1C

FIG. 1D

FIG. 2A

FIG. 2B

FIG. 4

FIG. 5A

FIG. 5B

FIG. 5C

FIG. 6A

FIG. 6B

FIG. 6C

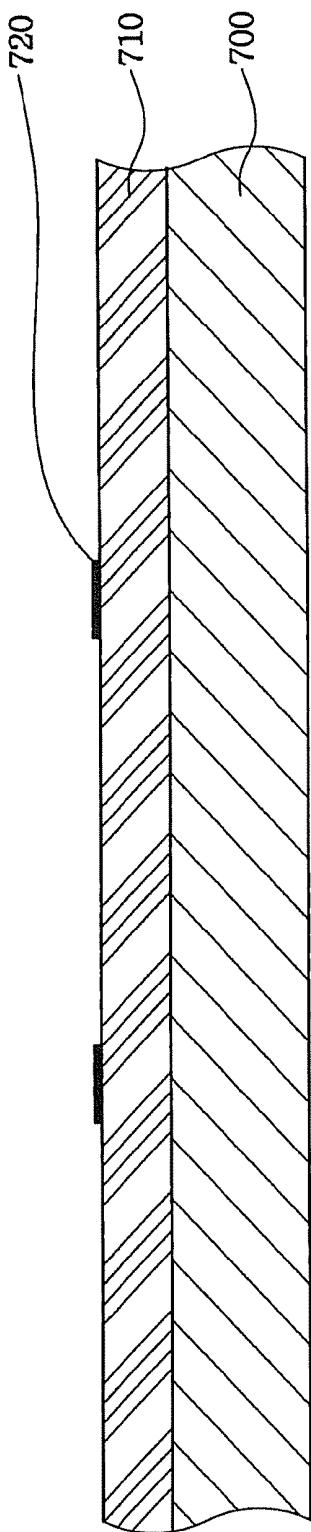

FIG. 7A

FIG. 7B

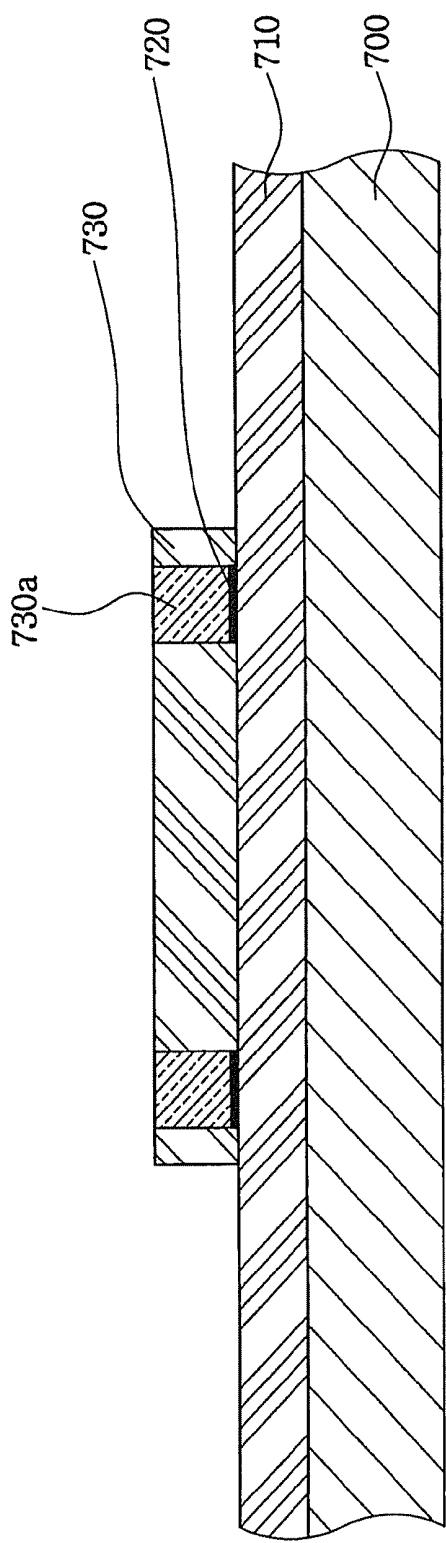

FIG. 7C

FIG. 8

FIG. 9

**METHOD OF FABRICATING

POLYCRYSTALLINE SILICON LAYER, TFT

FABRICATED USING THE SAME, METHOD

OF FABRICATING TFT, AND ORGANIC

LIGHT EMITTING DIODE DISPLAY DEVICE

HAVING THE SAME**

**CROSS-REFERENCE TO RELATED

APPLICATION**

**[0001]** This application claims the benefit of Korean Application No. 2007-53314, filed May 31, 2007, the disclosure of which is incorporated herein by reference.

**BACKGROUND OF THE INVENTION**

**[0002]** 1. Field of the Invention

**[0003]** Aspects of the present invention relate to a method of fabricating a polycrystalline silicon layer, a thin film transistor (TFT) fabricated using the same, a method of fabricating the TFT, and an organic light emitting diode (OLED) display device having the same. More particularly, aspects of the present invention relate to a method of fabricating a polycrystalline silicon layer, crystallized using crystallization-induced metal, wherein the method removes the crystallization-induced metal existing in a region of the polycrystalline silicon layer to be a channel by forming and annealing a metal layer or a silicide layer thereof. Aspects of the present invention further relate to a TFT having a semiconductor layer fabricated using the polycrystalline silicon layer formed by the method so as to significantly reduce a leakage current, a method of fabricating the TFT, and an OLED display device having the same.

**[0004]** 2. Description of the Related Art

**[0005]** Generally, polycrystalline silicon layers have been widely used as semiconductor layers for TFTs because they have a high field-effect mobility and can be applied to high speed circuits and constitute CMOS circuits. TFTs using polycrystalline silicon layers are typically used as active elements of active-matrix liquid crystal display (AMLCD) devices and switching and driving elements of OLEDs.

**[0006]** Methods of crystallizing an amorphous silicon layer into a polycrystalline silicon layer include solid phase crystallization (SPC), excimer laser crystallization (ELC), metal induced crystallization (MIC) and metal induced lateral crystallization (MILC). SPC is a method of annealing an amorphous silicon layer for several to several tens of hours at a temperature at or below the transition temperature of the glass used as a substrate of a display device employing a thin film transistor (typically, about 700° C. or less). ELC is a method of crystallizing an amorphous silicon layer by irradiating the amorphous silicon layer with an excimer laser and locally heating the amorphous silicon layer to a high temperature for very short time. MIC is a method of using phase transfer induction from amorphous silicon to polysilicon by contacting the amorphous silicon layer with metals such as nickel (Ni), palladium (Pd), gold (Au), and aluminum (Al), or implanting such metals into the amorphous silicon layer. MILC is a method of inducing sequential crystallization of an amorphous silicon layer by lateral diffusion of silicide formed by reacting metal with silicon.

**[0007]** However, SPC has disadvantages of a long processing time and a risk of transformation of the substrate due to the long processing time and high temperature used for the annealing. ELC has disadvantages in that expensive laser

equipment is required and interfacial characteristics between a semiconductor layer and a gate insulating layer may be poor due to protrusions generated on the created polycrystallized surface. MIC and MILC have disadvantages in that a large amount of crystallization-inducing metal remains on the crystallized polycrystalline silicon layer to increase the leakage current of a semiconductor layer of a TFT.

**[0008]** Recently, methods of crystallizing an amorphous silicon layer using metal have been widely being studied in order to develop a way to crystallize the amorphous silicon layer in a shorter time and at a lower temperature than SPC. The crystallization methods using metal include MIC and MILC, discussed above, and super grain silicon (SGS) crystallization, discussed below. However, methods of crystallization using a crystallization-inducing metal have a problem that characteristics of the TFT may deteriorate due to contamination by the crystallization-inducing metal.

**[0009]** Thus, after the amorphous silicon layer is crystallized using a crystallization-inducing metal, a gettering process may be performed to remove the crystallization-inducing metal. The gettering process is generally performed using an impurity such as phosphorous or a noble gas, or by a method of forming an amorphous silicon layer on a polycrystalline silicon layer. However, even by these methods, the crystallization-inducing metals may not be effectively removed from the polycrystalline silicon layer, and high leakage current may still be a problem.

**SUMMARY OF THE INVENTION**

**[0010]** Aspects of the present invention provide a method of fabricating a polycrystalline silicon layer crystallized using crystallization-inducing metal by removing the crystallization-inducing metal remaining in a region of the polycrystalline silicon layer to be a channel, a thin film transistor (TFT) having a semiconductor layer formed of the polycrystalline silicon layer formed by the method so as to significantly lower leakage current, a method of fabricating the same, and an organic light emitting diode (OLED) display device using the same.

**[0011]** According to an embodiment of the present invention, a method of removing a crystallization-inducing metal from a first predetermined region of a polycrystalline silicon layer crystallized using a crystallization-inducing metal includes providing a metal layer pattern or metal silicide layer pattern in contact with the polycrystalline silicon layer in a second predetermined region of the polycrystalline silicon layer; and performing annealing to getter the crystallization-inducing metal existing in the first predetermined region to the second predetermined region.

**[0012]** According to another embodiment of the present invention, a method of fabricating a polycrystalline silicon layer includes forming an amorphous silicon layer on a substrate; crystallizing the amorphous silicon layer into a polycrystalline silicon layer using crystallization-inducing metal; forming a metal layer pattern or metal silicide layer pattern in contact with an upper or lower region of the polycrystalline silicon layer corresponding to a region excluding a channel region in the polycrystalline silicon layer; and annealing the substrate to getter the crystallization-inducing metal existing in the channel region in the polycrystalline silicon layer to a region in the polycrystalline silicon layer corresponding to the metal layer pattern or metal silicide layer pattern.

**[0013]** According to another embodiment of the present invention, a TFT includes a substrate; a semiconductor layer

disposed on the substrate and including a channel region, and source and drain regions; a metal layer pattern or metal silicide layer pattern disposed over or under the semiconductor layer corresponding to a region excluding the channel region; a gate electrode disposed to correspond to the channel region of the semiconductor layer; a gate insulating layer interposed between the gate electrode and the semiconductor layer to insulate the semiconductor layer from the gate electrode; and source and drain electrodes electrically connected to the source and drain regions of the semiconductor layer.

[0014] According to still another embodiment of the present invention, a method of fabricating a TFT includes preparing a substrate; forming an amorphous silicon layer on the substrate; crystallizing the amorphous silicon layer into a polycrystalline silicon layer using crystallization-inducing metal; forming a metal layer pattern or metal silicide layer pattern in contact with an upper or lower region of the polycrystalline silicon layer corresponding to a region excluding a channel region in the polycrystalline silicon layer; forming a gate electrode corresponding to the channel region of the polycrystalline silicon layer; forming a gate insulating layer between the gate electrode and the polycrystalline silicon layer to insulate the polycrystalline silicon layer from the gate electrode; forming source and drain electrodes electrically connected to source and drain regions of the polycrystalline silicon layer; and after forming the metal layer pattern or metal silicide layer pattern, annealing the substrate to getter the crystallization-inducing metal existing in the channel region of the polycrystalline silicon layer to a region of the polycrystalline silicon layer corresponding to the metal layer pattern or metal silicide layer pattern.

[0015] According to yet another embodiment of the present invention, an OLED display device includes: a substrate; a semiconductor layer disposed on the substrate, and including a channel region and source and drain regions; a metal layer pattern or metal silicide layer pattern disposed over or under the semiconductor layer corresponding to a region excluding the channel region; a gate electrode disposed to correspond to the channel region of the semiconductor layer; a gate insulating layer interposed between the gate electrode and the semiconductor layer to insulate the semiconductor layer from the gate electrode; source and drain electrodes electrically connected to the source and drain regions of the semiconductor layer; a first electrode electrically connected to one of the source and drain electrodes; an organic layer disposed on the first electrode; and a second electrode disposed on the organic layer.

[0016] Additional aspects and/or advantages of the invention will be set forth in part in the description which follows and, in part, will be obvious from the description, or may be learned by practice of the invention.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0017] These and/or other aspects and advantages of the invention will become apparent and more readily appreciated from the following description of the embodiments, taken in conjunction with the accompanying drawings of which:

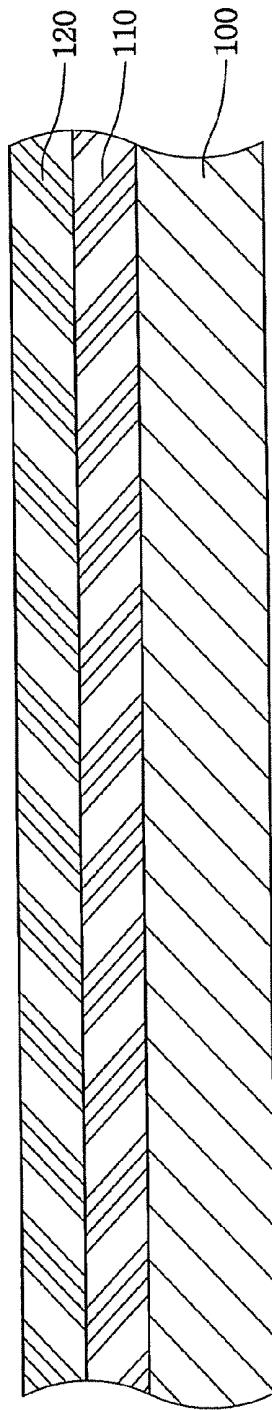

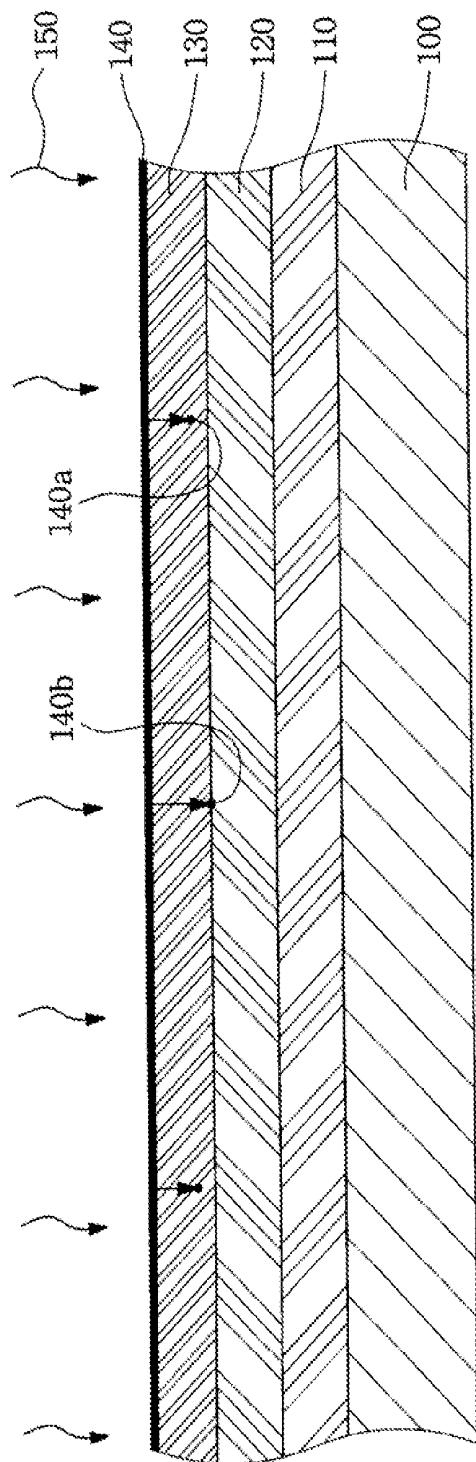

[0018] FIGS. 1A to 1D are cross-sectional views illustrating a crystallization process according to an embodiment of the present invention;

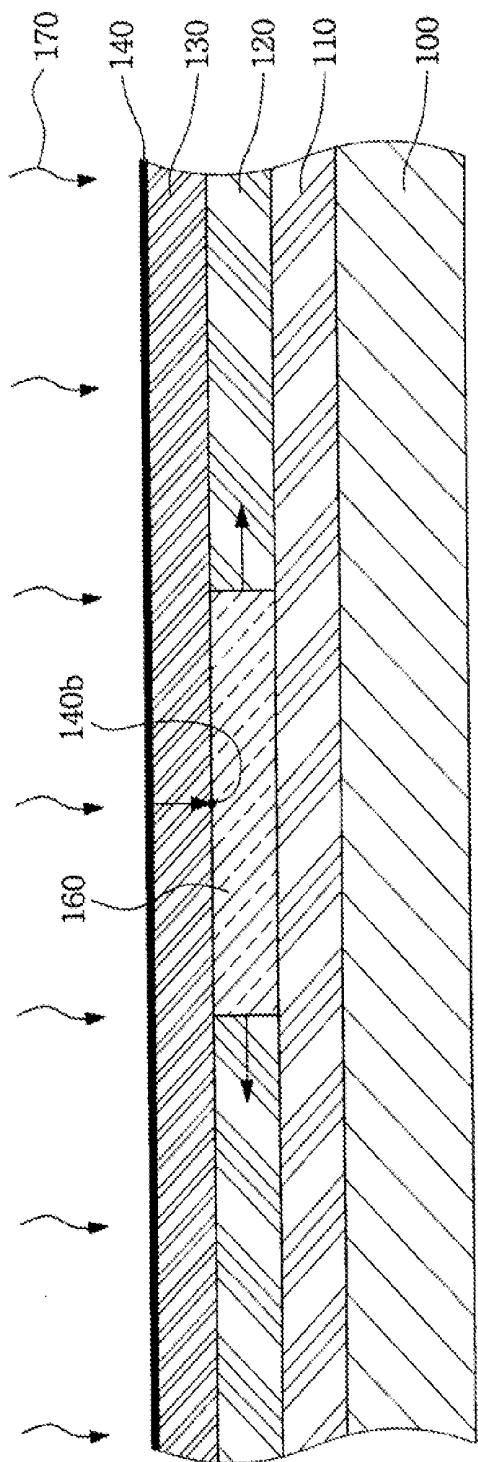

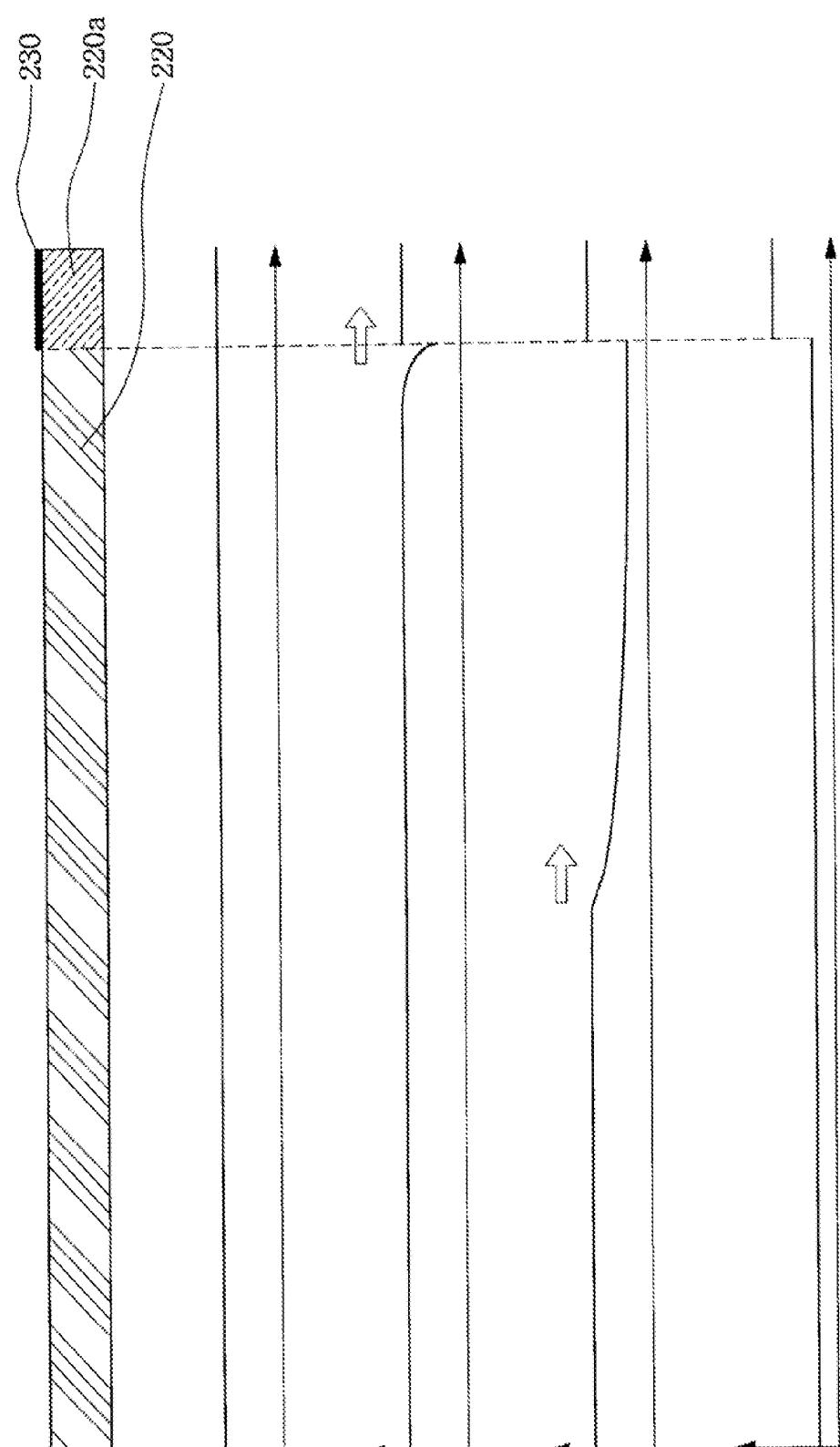

[0019] FIGS. 2A and 2B are cross-sectional views illustrating a process of removing crystallization-inducing metal remaining in a region of a polycrystalline silicon layer to be a

channel using a method of fabricating the polycrystalline silicon layer according to an embodiment of the present invention;

[0020] FIGS. 3A to 3E are cross-sectional views illustrating a polycrystalline silicon layer and a mechanism of gettering crystallization-inducing metal in the polycrystalline silicon layer;

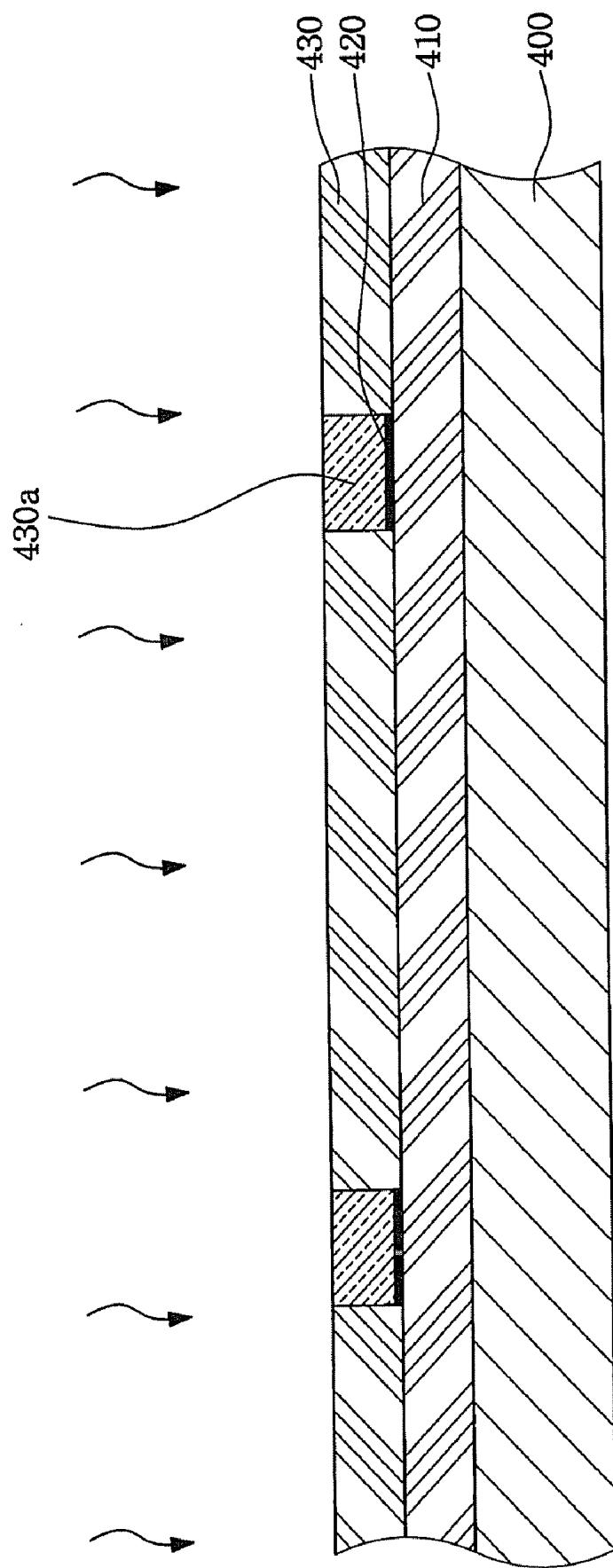

[0021] FIG. 4 is a cross-sectional view illustrating a process of removing crystallization-inducing metal remaining in a region of a polycrystalline silicon layer to be a channel using a method of fabricating the polycrystalline silicon layer according to another embodiment of the present invention;

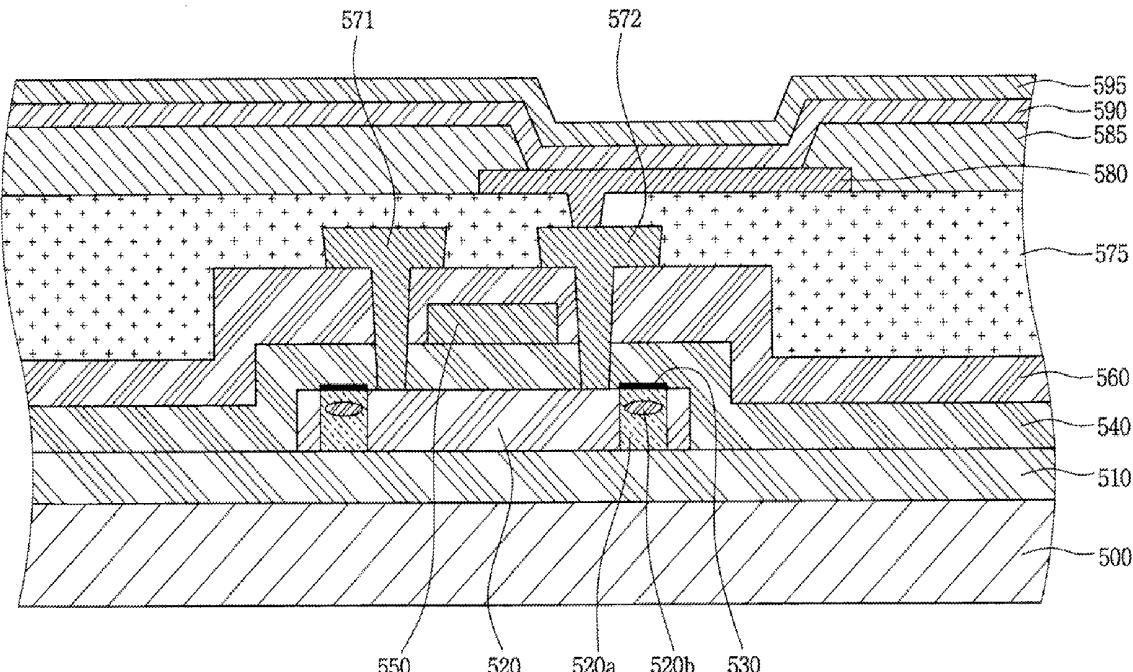

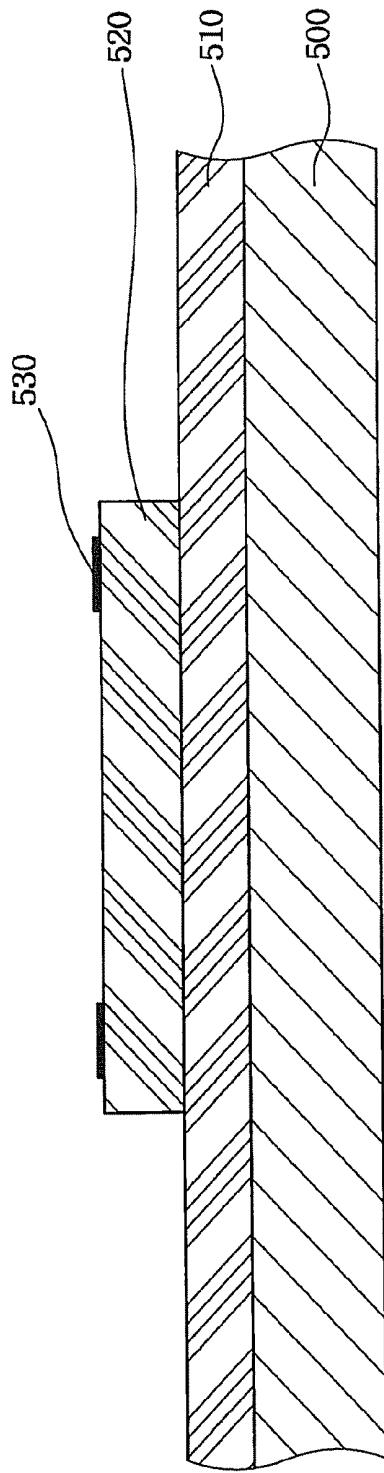

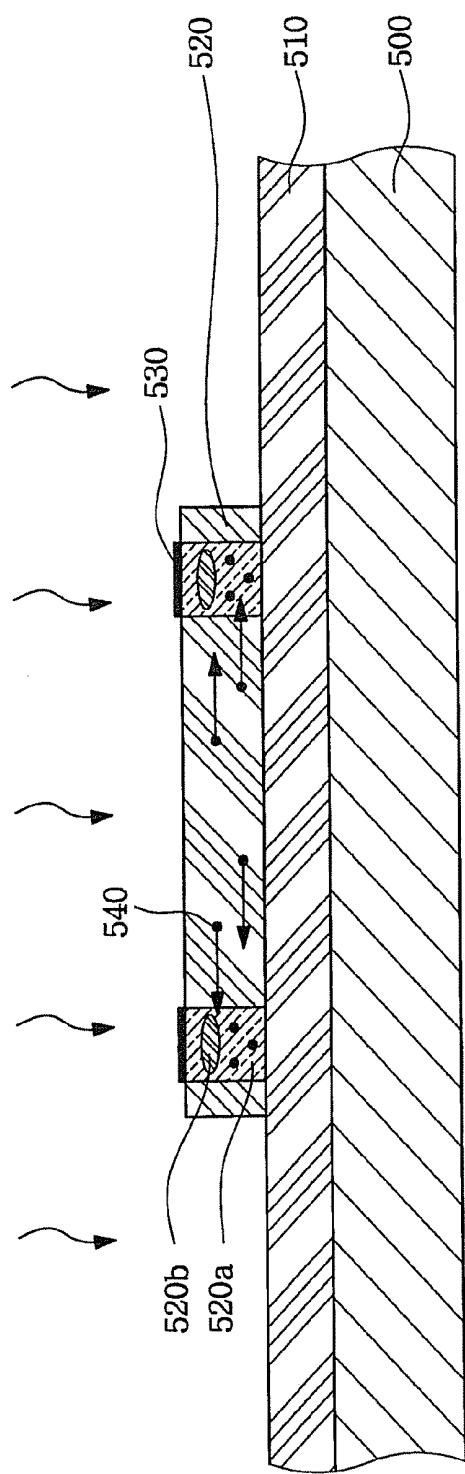

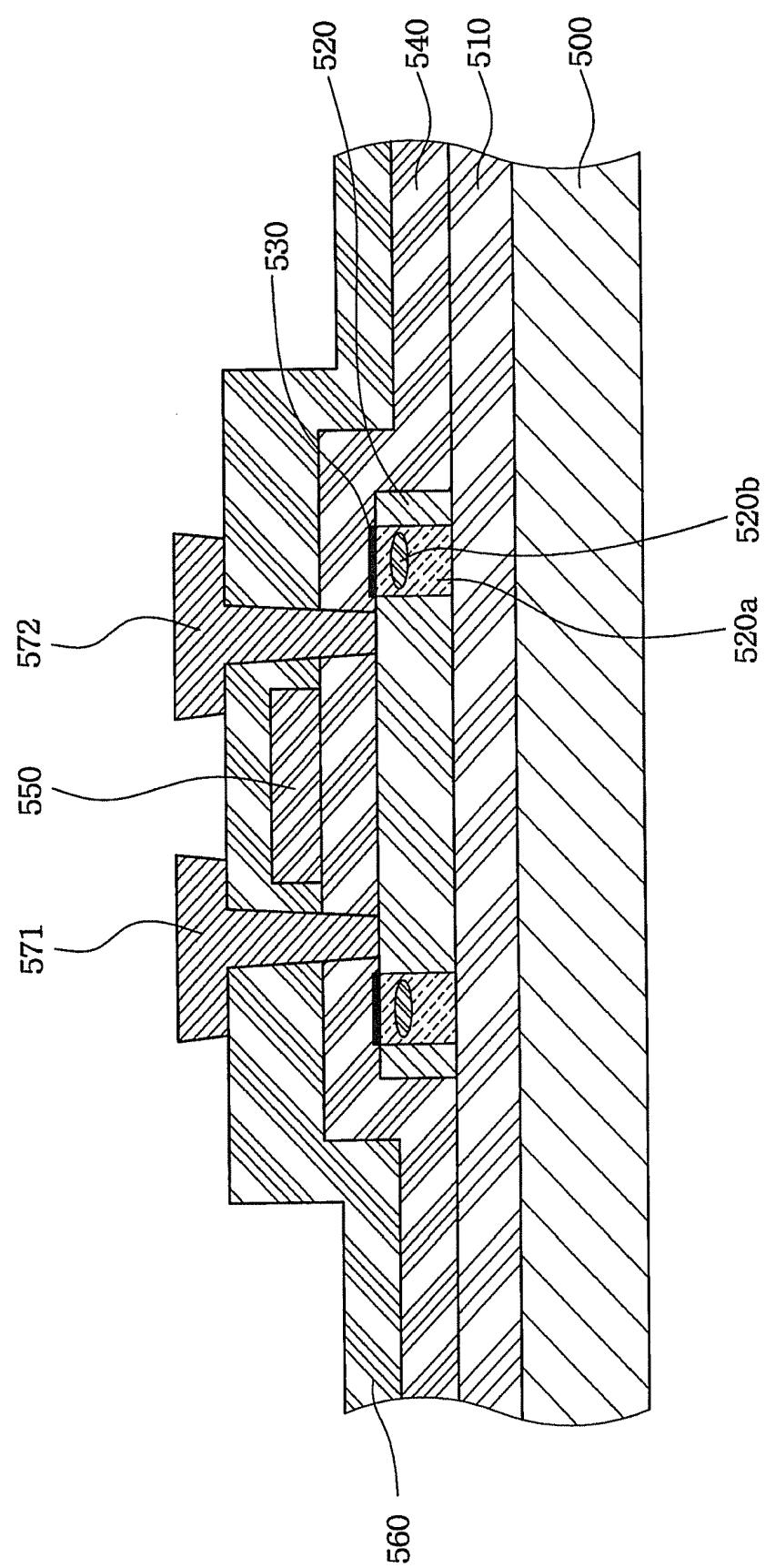

[0022] FIGS. 5A to 5C are cross-sectional views illustrating a process of fabricating a top-gate thin film transistor using the method of fabricating the polycrystalline silicon layer according to FIGS. 2A and 2B;

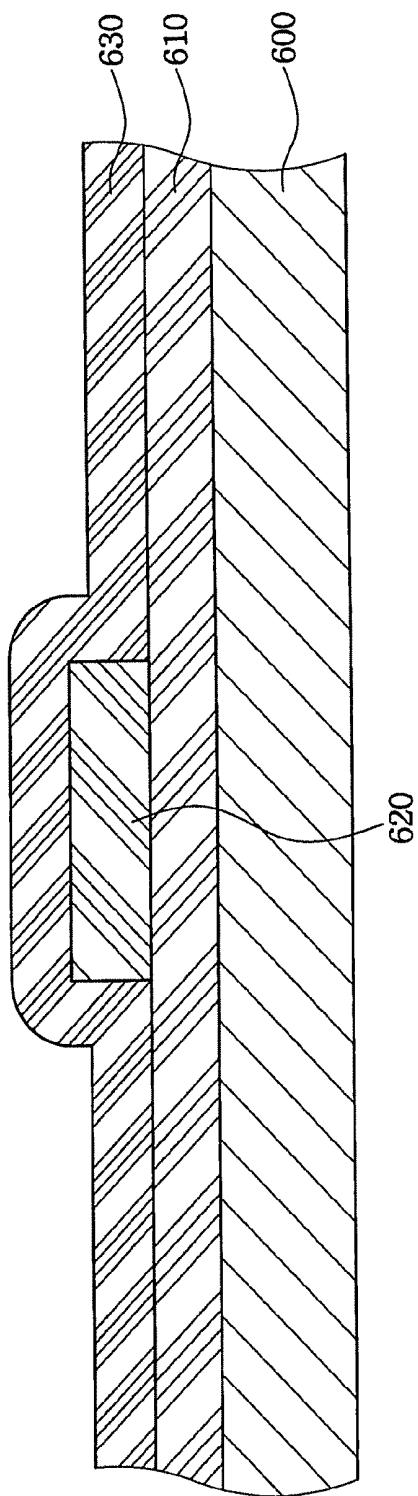

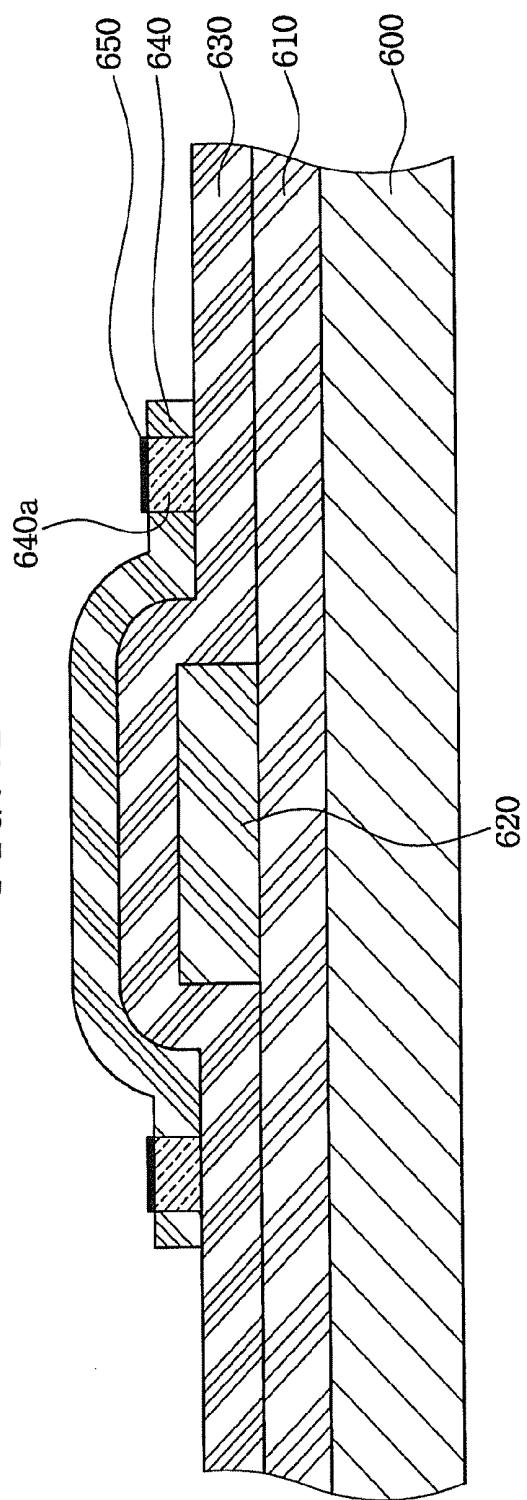

[0023] FIGS. 6A to 6C are cross-sectional views illustrating a process of fabricating a bottom-gate thin film transistor using the method of fabricating the polycrystalline silicon layer according to the FIGS. 2A and 2B;

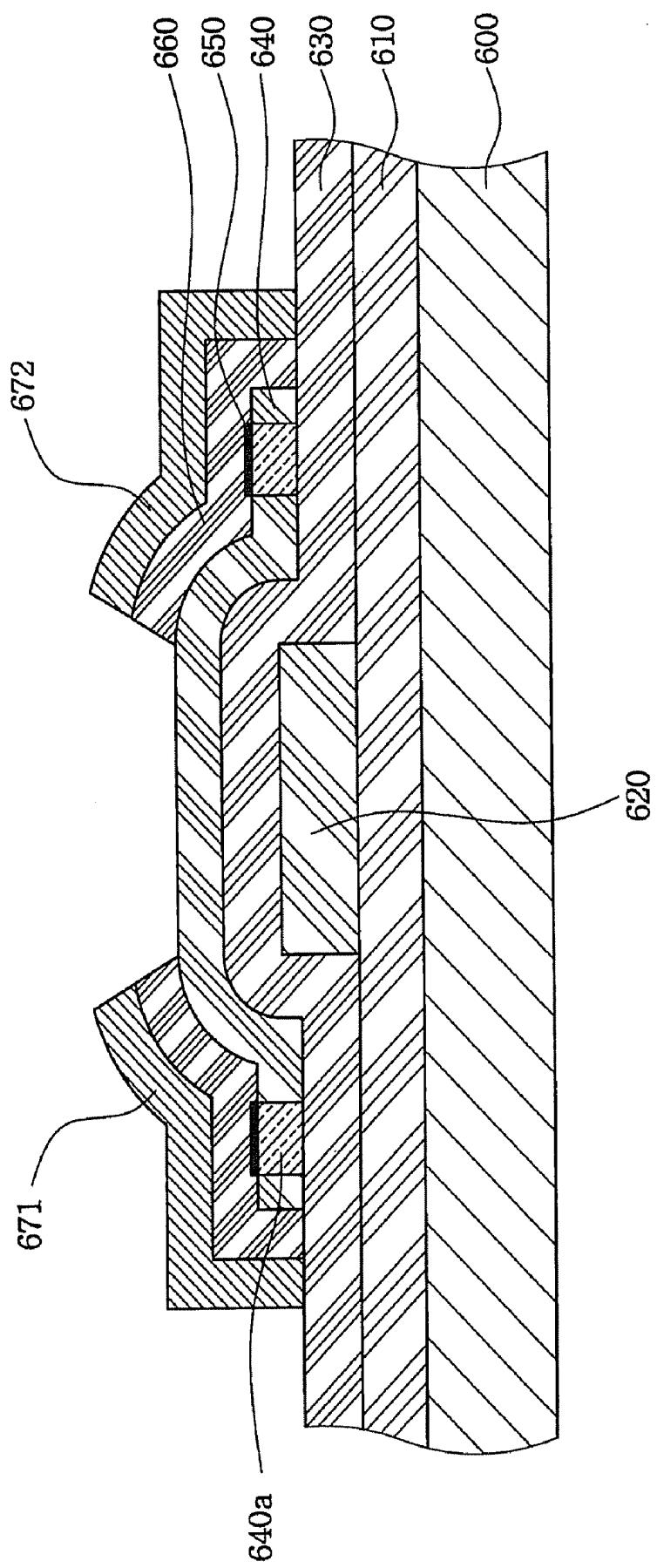

[0024] FIGS. 7A to 7C are cross-sectional views illustrating a process of fabricating a top-gate thin film transistor using the method of fabricating the polycrystalline silicon layer according to FIG. 4;

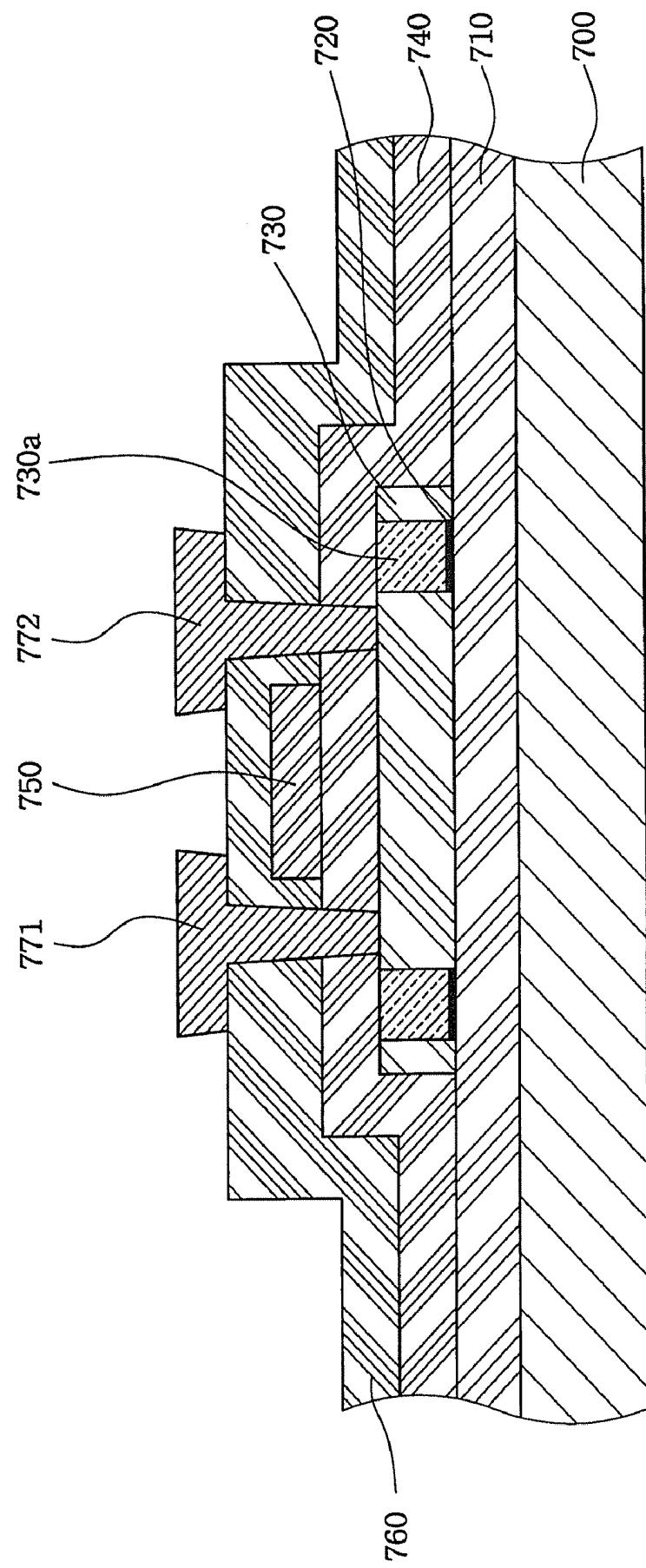

[0025] FIG. 8 is a comparison graph of off-current values per unit width between semiconductor layers of a thin film transistor formed by a method of fabricating a polycrystalline silicon layer according to an exemplary embodiment of the present invention, and a thin film transistor formed by a conventional gettering method by phosphorous-doping; and

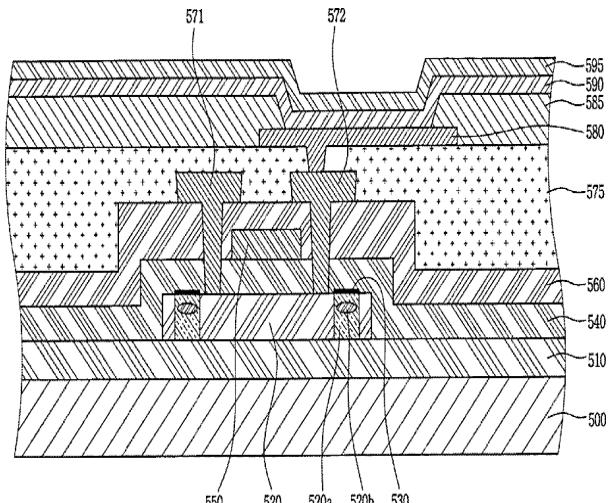

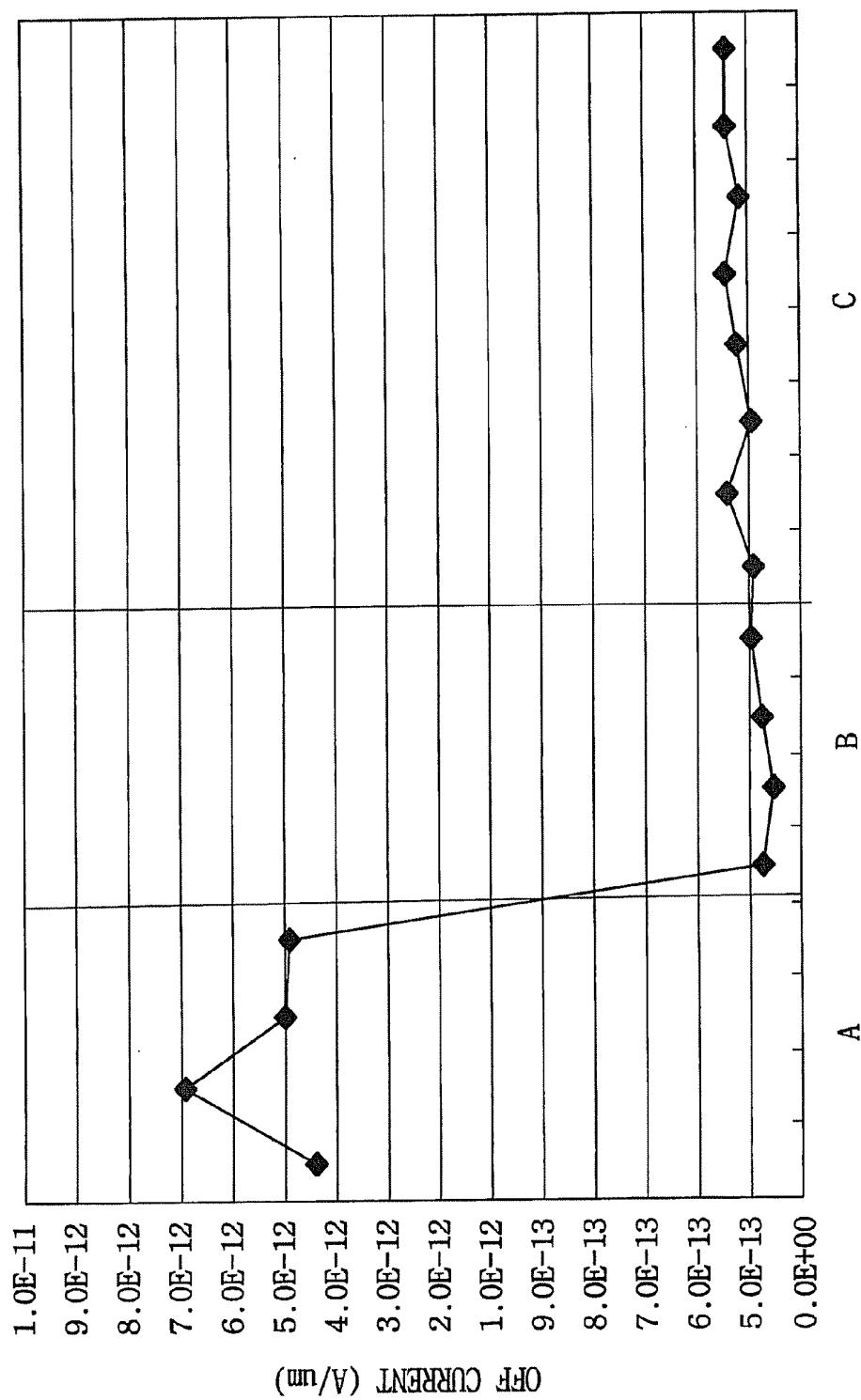

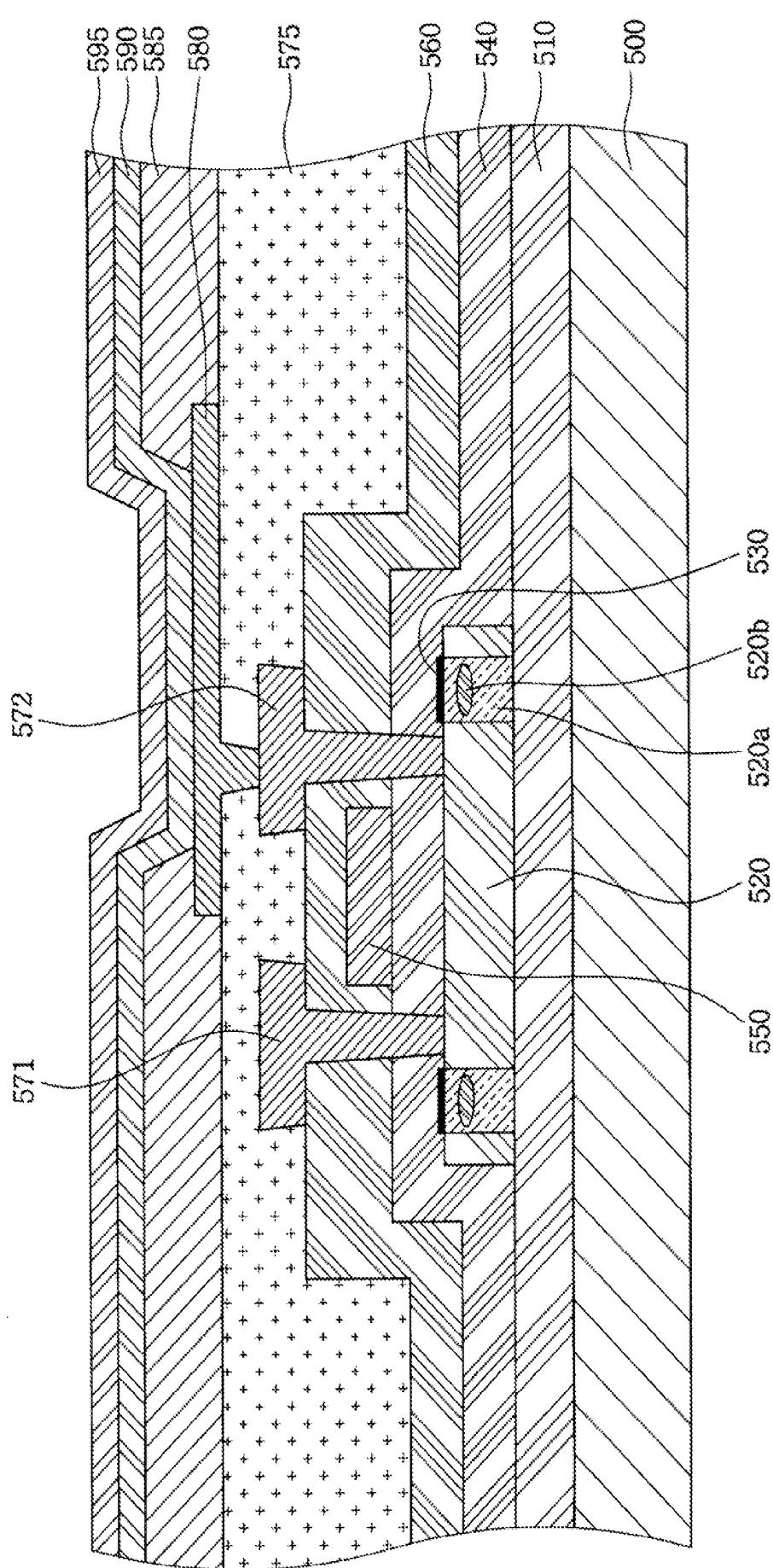

[0026] FIG. 9 is a cross-sectional view of an organic light emitting diode (OLED) display device including a thin film transistor formed by the method of fabricating the polycrystalline silicon layer according to FIGS. 2A and 2B.

#### DETAILED DESCRIPTION OF THE EMBODIMENTS

[0027] Reference will now be made in detail to the present embodiments of the present invention, examples of which are illustrated in the accompanying drawings, wherein like reference numerals refer to the like elements throughout. The embodiments are described below in order to explain the present invention by referring to the figures.

[0028] FIGS. 1A to 1D are cross-sectional views illustrating a crystallization process according to an embodiment of the present invention.

[0029] First, as illustrated in FIG. 1A, a buffer layer 110 may be formed on a substrate 100, which is formed of glass or plastic. The buffer layer 110 is an insulating layer and may be formed of silicon oxide, silicon nitride or a combination thereof by chemical vapor deposition (CVD) or physical vapor deposition (PVD). The buffer layer 110 serves to prevent the diffusion of moisture or impurities occurring in the substrate 100 or to adjust the heat transfer rate during crystallization, thereby allowing crystallization of an amorphous silicon layer to proceed easily.

[0030] Subsequently, an amorphous silicon layer 120 is formed on the buffer layer 110. As non-limiting examples, the amorphous silicon layer 120 may be formed by CVD or PVD. Also, during or after forming the amorphous silicon layer 120, a dehydrogenation process may be performed to lower the concentration of hydrogen.

[0031] Then, the amorphous silicon layer 120 is crystallized into a polycrystalline silicon layer. According to aspects

of the present invention, the amorphous silicon layer is crystallized into a polycrystalline silicon layer by a crystallization method using a crystallization-inducing metal, such as a metal induced crystallization (MIC) technique, a metal induced lateral crystallization (MILC) technique or a super grain silicon (SGS) technique.

[0032] The SGS technique is a method of crystallizing an amorphous silicon layer in which the concentration of the crystallization-inducing metal diffused into the amorphous silicon layer is lowered in order to control the grain size of the polycrystalline silicon to be within the range of several  $\mu\text{m}$  to several hundreds of  $\mu\text{m}$ . In general, lowering the concentration of the crystallization-inducing metal increases the grain size of the polycrystalline silicon produced by spacing out the sites from which crystallization proceeds. To lower the concentration of crystallization-inducing metal diffused into the amorphous silicon layer, a capping layer may be formed on the amorphous silicon layer, and a crystallization-inducing metal layer may be formed on the capping layer and annealed to diffuse the crystallization-inducing metal into the amorphous silicon layer in a controlled manner. Alternatively, a thin crystallization-inducing metal layer may be provided in order to diffuse into the amorphous silicon layer at a low concentration without the need to form the capping layer on the amorphous silicon layer.

[0033] As a specific, non-limiting example, the polycrystalline silicon layer is preferably formed by an SGS crystallization technique, which will now be described.

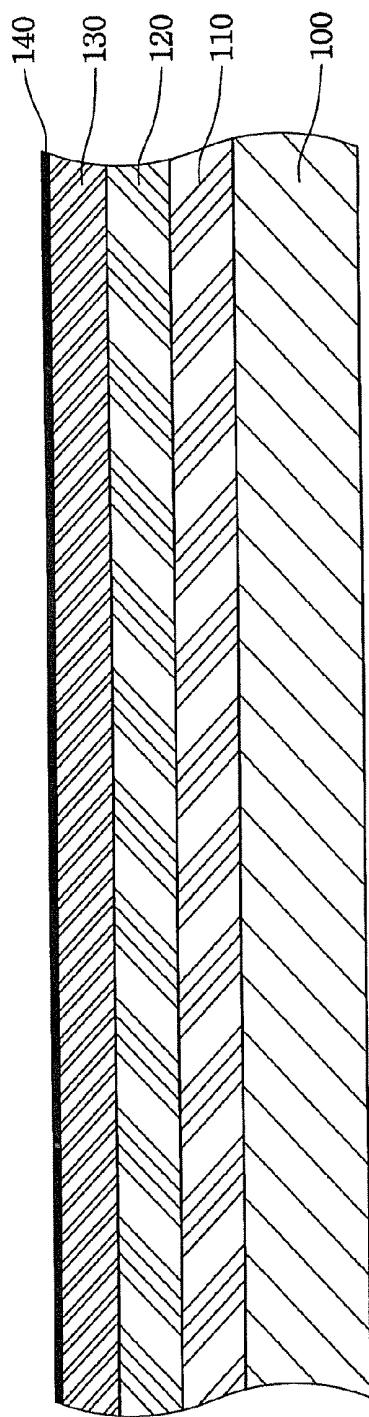

[0034] FIG. 1B is a cross-sectional view illustrating a process of forming a capping layer and a crystallization-inducing metal layer on the amorphous silicon layer. Referring to FIG. 1B, a capping layer 130 is formed on the amorphous silicon layer 120. The capping layer 130 may be formed of any material through which a crystallization metal may diffuse through annealing such as, for example, silicon nitride or a combination of silicon nitride and silicon oxide. The capping layer 130 is formed by any suitable deposition method such as, for example, CVD or PVD. As a non-limiting example, the capping layer 130 may be formed to a thickness of 1 to 2000  $\text{\AA}$ . When the thickness of the capping layer 130 is less than 1  $\text{\AA}$ , it may be difficult to control the amount of crystallization-inducing metal that diffuses through the capping layer 130. When the thickness of the capping layer 130 is more than 2000  $\text{\AA}$ , the amount of the crystallization-inducing metal that diffuses into the amorphous silicon layer 120 may be too small, such that it may be difficult to crystallize the amorphous silicon layer into a polycrystalline silicon layer.

[0035] Subsequently, a crystallization-inducing metal is deposited on the capping layer 130 to form a crystallization-inducing metal layer 140. As non-limiting examples, the crystallization-inducing metal may be selected from the group consisting of nickel (Ni), palladium (Pd), silver (Ag), gold (Au), aluminum (Al), tin (Sn), antimony (Sb), copper (Cu), terbium (Tb) and cadmium (Cd), and Ni. As a specific, non-limiting example, the crystallization-inducing metal may be Ni. As a non-limiting example, the crystallization-inducing metal layer 140 may be formed to have a surface density of  $10^{11}$  to  $10^{15}$  atoms/ $\text{cm}^2$  on the capping layer 130. When the crystallization-inducing metal is formed with a surface density of less than  $10^{11}$  atoms/ $\text{cm}^2$ , the amount of a seed, i.e., a crystallization core, may be too small, and thus it may be difficult to crystallize the amorphous silicon layer into a polycrystalline silicon layer by the SGS crystallization technique. When the crystallization-inducing metal is formed with a

surface density of more than  $10^{15}$  atoms/ $\text{cm}^2$ , the amount of crystallization-inducing metal diffused into the amorphous silicon layer may be too large, such that the grains produced in the polycrystalline silicon layer are smaller in size. The amount of crystallization-inducing metal remaining in the polycrystalline layer also increases, and thus the characteristics of a semiconductor layer formed by patterning the polycrystalline silicon layer deteriorate.

[0036] FIG. 1C is a cross-sectional view illustrating a process of diffusing the crystallization-inducing metal through the capping layer to an interface of the amorphous silicon layer by annealing the substrate. Referring to FIG. 1C, the substrate 100 having the buffer layer 110, the amorphous silicon layer 120, the capping layer 130 and the crystallization-inducing metal layer 140 is annealed 150 to move some of the crystallization-inducing metal of the crystallization-inducing metal layer 140 to the surface of the amorphous silicon layer 120. That is, only a very small amount of crystallization-inducing metal 140b from the metal layer 140 diffuses through the capping layer 130 to the surface of the amorphous silicon layer 120 during the annealing, and most of the crystallization-inducing metal 140a does not reach the amorphous silicon layer 120, or does not pass at all through the capping layer 130.

[0037] Thus, the amount of crystallization-inducing metal reaching the surface of the amorphous silicon layer 120 is determined by the diffusion blocking ability of the capping layer 130, which is closely related to the thickness and/or the density of the capping layer 130. That is, as the thickness and/or the density of the capping layer 130 increases, the diffused amount of the crystallization inducing metal decreases, and thus the produced grains become larger. On the other hand, if the thickness and/or the density of the capping layer 130 decreases, the diffused amount of the crystallization inducing metal increases, and thus the produced grains become smaller.

[0038] The annealing process 150 may be performed for several seconds to several hours at a temperature of 200 to 900° C. to diffuse the crystallization-inducing metal. The annealing conditions are not limited to those described herein and may be selected to prevent a transformation of the substrate caused by excessive annealing and to enhance production costs and yield. The annealing process 150 may be one of a furnace process, a rapid thermal annealing (RTA) process, an UV process and a laser process, as non-limiting examples.

[0039] FIG. 1D is a cross-sectional view illustrating a process of crystallizing the amorphous silicon layer into a polycrystalline silicon layer by using the diffused crystallization-inducing metal. Referring to FIG. 1D, the amorphous silicon layer 120 is crystallized into a polycrystalline silicon layer 160 by the crystallization-inducing metals 140b that have diffused to the surface of the amorphous silicon layer 120 through the capping layer 130. That is, the diffused crystallization-inducing metal 140b bonds with silicon of the amorphous silicon layer to form metal silicide, which forms a crystallization core, i.e., a seed, and thus the amorphous silicon layer is crystallized from the seed into the polycrystalline silicon layer.

[0040] An annealing process 170 may be performed without removing the capping layer 130 and the crystallization-inducing metal layer 140, as shown in FIG. 1D. Alternatively, the polycrystalline silicon layer may be formed by diffusing the crystallization-inducing metal onto the amorphous silicon layer 120 to form metal silicide, which is a crystallization

core, removing the capping layer 130 and the crystallization-inducing metal layer 140 and then annealing the bared amorphous silicon layer.

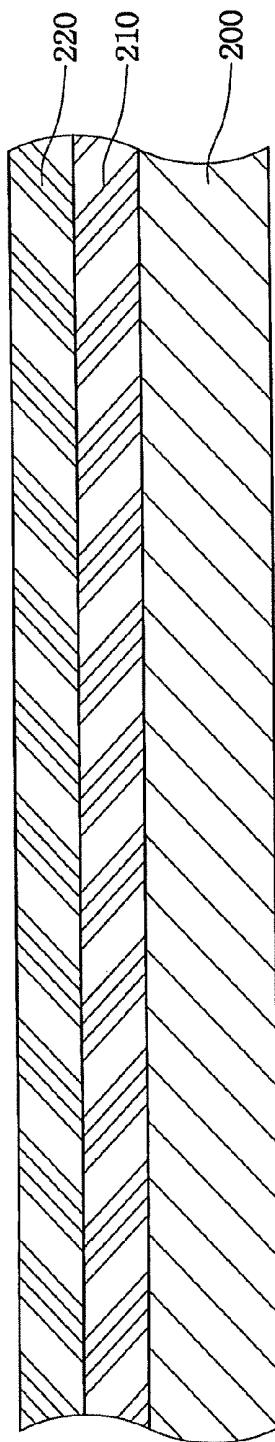

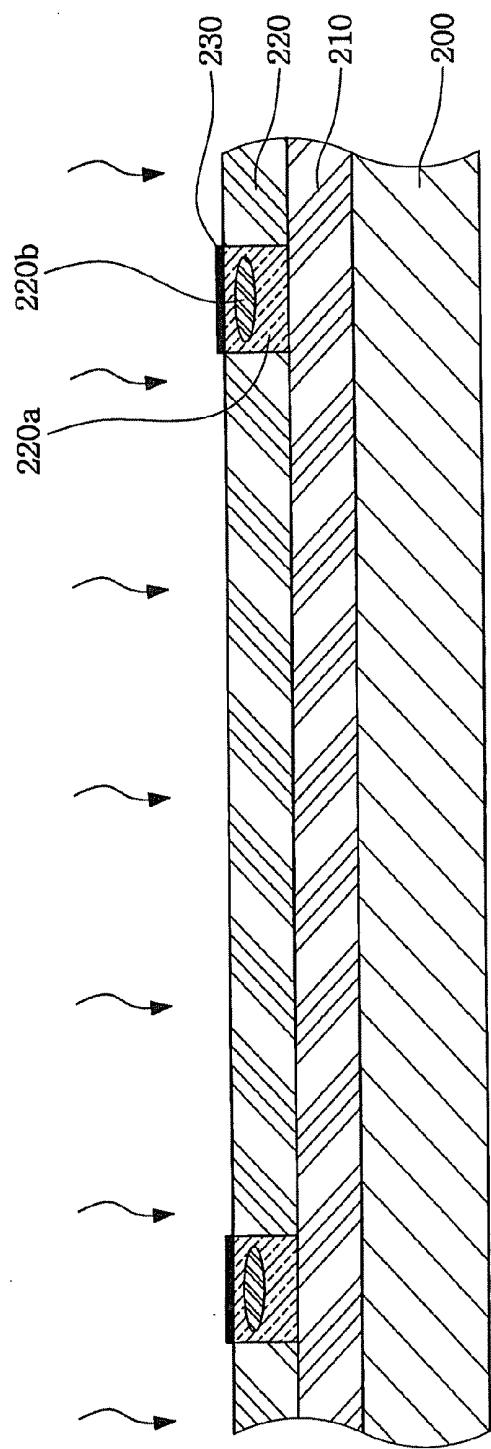

[0041] FIGS. 2A and 2B are cross-sectional views illustrating a process of fabricating a polycrystalline silicon layer according to a first embodiment of the present invention.

[0042] First, as illustrated in FIG. 2A, a substrate 200 having a buffer layer 210 and a polycrystalline silicon layer 220 formed by crystallizing an amorphous silicon layer using crystallization-inducing metal as shown in FIGS. 1A to 1D is provided.

[0043] Subsequently, as illustrated in FIG. 2B, a metal layer pattern or metal silicide layer pattern 230 is formed on a predetermined region of the polycrystalline silicon layer 220. The predetermined region is selected as a region excluding a channel region in the finished TFT. The metal layer pattern or metal silicide layer pattern 230 is formed of a metal having a smaller diffusion coefficient in the polycrystalline silicon layer 220 than that of the crystallization-inducing metal or an alloy thereof, or silicide thereof. The metal or metal silicide of the metal layer pattern or metal silicide layer pattern 230 is selected for gettering properties, so that the crystallization-inducing metal is gettered to a region 220a in the polycrystalline silicon layer 220 corresponding to the metal layer pattern or metal silicide layer pattern 230.

[0044] The diffusion coefficient of metal or metal silicide of the metal layer pattern or metal silicide layer pattern 230 in the polycrystalline silicon layer 220 may be  $1/100$  or less of that of the crystallization-inducing metal. When the diffusion coefficient of the metal or metal silicide is  $1/100$  or less of that of the crystallization-inducing metal, the metal or metal silicide for gettering may be prevented from diffusing to another region in the polycrystalline silicon layer 220 from the region 220a corresponding to the metal layer pattern or metal silicide layer pattern 230.

[0045] Ni is widely used as the crystallization-inducing metal for crystallization into a polycrystalline silicon layer. Since Ni has a diffusion coefficient in polycrystalline silicon of approximately  $10^{-5} \text{ cm}^2/\text{s}$  or less, the diffusion coefficient of the metal or metal silicide of the metal layer pattern or metal silicide layer pattern 230 used for gettering in a polycrystalline silicon layer crystallized by Ni may be  $1/100$  or less of that of Ni, i.e., from 0 to  $10^{-7} \text{ cm}^2/\text{s}$ . As non-limiting examples, the metal layer pattern or metal silicide layer pattern 230 may include one selected from the group consisting of scandium (Sc), titanium (Ti), zirconium (Zr), hafnium (Hf), vanadium (V), niobium (Nb), tantalum (Ta), chromium (Cr), molybdenum (Mo), tungsten (W), manganese (Mn), rhenium (Re), ruthenium (Ru), osmium (Os), cobalt (Co), rhodium (Rh), iridium (Ir), platinum (Pt), yttrium (Y), lanthanum (La), cerium (Ce), praseodymium (Pr), neodymium (Nd), dysprosium (Dy), holmium (Ho), titanium nitride (TiN), tantalum nitride (TaN), and an alloy thereof, or a silicide thereof.

[0046] The metal layer pattern or metal silicide layer pattern 230 may be formed on the polycrystalline silicon layer 220 to be spaced 50  $\mu\text{m}$  or less apart from a region that will become a channel in the polycrystalline silicon layer 220. When the pattern 230 is formed to be spaced more than 50  $\mu\text{m}$  apart from a channel region, the crystallization-inducing metal existing in the channel region has to diffuse farther to be gettered in region 220a corresponding to the pattern 230. Consequently, it may be necessary to anneal the substrate for

a longer time, thereby transforming the substrate and making it difficult to diffuse the crystallization inducing metal to the region.

[0047] As a non-limiting example, the metal layer pattern or metal silicide layer pattern 230 may be formed to a thickness of 30 to 10000  $\text{\AA}$ . When the thickness of the pattern 230 is less than 30  $\text{\AA}$ , the crystallization-inducing metal may not be effectively gettered in the region 220a of the polycrystalline silicon layer 220 corresponding to the metal layer pattern or metal silicide layer pattern 230. When the thickness of the pattern 230, is more than 10000  $\text{\AA}$ , the pattern 230 may be too thick, and thus, peeling of the layers may occur due to stress.

[0048] When the metal layer pattern or metal silicide layer pattern 230 is formed by depositing a metal layer or a metal silicide layer only on a predetermined region of the polycrystalline silicon layer 220 and is then annealed for a subsequent gettering process, the metal layer pattern or metal silicide layer pattern 230 may be formed to a thickness of 30 to 10000  $\text{\AA}$ .

[0049] Alternatively, the metal layer pattern or metal silicide layer pattern 230 may be formed to be in contact with a predetermined region of the polycrystalline silicon layer 220 by forming an intermediate layer on the polycrystalline silicon layer 220, forming a hole in the intermediate layer to expose the predetermined region and depositing a metal layer or a metal silicide layer on the entire surface of the intermediate layer and the exposed region. The metal layer or the metal silicide layer formed as such may be thermally expanded by annealing for the subsequent gettering to transform the substrate 200, and thus the metal layer pattern or metal silicide layer pattern 230 may be formed to a thickness of 30 to 2000  $\text{\AA}$ .

[0050] Then, the substrate 200 having the buffer layer 210, the polycrystalline silicon layer 220, and the metal layer pattern or metal silicide layer pattern 230 is annealed. The annealing process is performed to getter crystallization-inducing metal in a channel region of the polycrystalline silicon layer 220 by diffusing the crystallization-inducing metal to the region 220a in the polycrystalline silicon layer 220 corresponding to metal layer pattern or metal silicide layer pattern 230. The annealing process may be performed for 10 seconds to 10 hours. If Ni was used as the crystallization-inducing metal, the annealing may be performed at a temperature of 500 to 993  $^{\circ}\text{C}$ . In particular, Ni may be difficult to diffuse to a predetermined region in the polycrystalline silicon layer 220 at less than 500  $^{\circ}\text{C}$ ., and may exist in a liquid phase at more than 993  $^{\circ}\text{C}$ ., a eutectic point of Ni.

[0051] Also, when the annealing time is less than 10 seconds, it may be difficult to sufficiently remove the crystallization-inducing metal from the channel region of the polycrystalline silicon layer 220. When the annealing time is more than 10 hours, the substrate 200 may be transformed due to the long annealing time, which is not desirable for production cost and yield.

[0052] Further, in order to improve the gettering effect, an n-type impurity or a p-type impurity may be implanted into the region 220a in the polycrystalline silicon layer 220 corresponding to the metal layer pattern or metal silicide layer pattern 230. As non-limiting examples, the n-type impurity may be phosphorous (P), and the p-type impurity may be boron (B). Also, the gettering effect may be improved by forming a damage region 220b using ions or plasma in the

region **220a** in the polycrystalline silicon layer **220** corresponding to the metal layer pattern or metal silicide layer pattern **230**.

[0053] FIGS. 3A to 3E illustrate a polycrystalline silicon layer and a mechanism of gettering the crystallization-inducing metal in the polycrystalline silicon layer **220** using the metal layer pattern or metal silicide layer pattern **230**. In particular, FIG. 3A is a cross-section of a polycrystalline silicon layer having a metal layer pattern or metal silicide layer pattern **230** and a region **220a** in the polycrystalline silicon layer **220** corresponding to the metal layer pattern or metal silicide layer pattern **230**. FIGS. 3B to 3E are graphs that represent the concentration of the crystallization-inducing metal at the corresponding lateral positions of the polycrystalline silicon layer **220** of FIG. 3A at successive periods of time before (FIG. 3B), during (FIG. 3C to 3D) and after (FIG. 3E) the annealing.

[0054] First, referring to FIG. 3B, before annealing the substrate **200**, the concentration of the crystallization-inducing metal in the polycrystalline silicon layer **220** is constant. During annealing, in the case of a metal layer pattern **230**, the metal of the metal layer pattern **230** bonds with silicon of the polycrystalline silicon layer **220** to form a metal silicide in the region **220a** in the polycrystalline silicon layer **220** corresponding to the metal layer pattern or metal silicide layer pattern **230**; in the case of a metal silicide layer pattern, the metal silicide of the metal silicide layer pattern moves to the region **220a** in the polycrystalline silicon layer **220**. Moreover, when the substrate **200** is annealed, the crystallization-inducing metal existing in the polycrystalline silicon layer **220**, and which has a high diffusion coefficient in the polycrystalline silicon layer **220**, begins to randomly diffuse in the polycrystalline silicon layer **220**.

[0055] During the annealing, when the randomly moving crystallization-inducing metal diffuses into the region **220a** in the polycrystalline silicon layer **220** corresponding to the metal layer pattern or metal silicide layer pattern **230**, the crystallization-inducing metal in the region **220a** having the different metal silicide is thermodynamically more stable than the crystallization-inducing metal in a region in the polycrystalline silicon layer having no metal layer pattern or metal silicide layer pattern **230**. Thus, the crystallization-inducing metal that diffuses to the region **220a** cannot escape.

[0056] As a result, referring to FIG. 3C, the concentration of the crystallization-inducing metal in the polycrystalline silicon layer **220** adjacent to the region **220a** corresponding to the metal layer pattern or metal silicide layer pattern **230** gradually decreases, and thus a concentration difference occurs between the region **220a** and a region far from the region **220a** in the polycrystalline silicon layer **220**.

[0057] Referring to FIG. 3D, due to the concentration difference, the crystallization-inducing metal in the polycrystalline layer **220** far away from the region **220a** corresponding to the metal layer pattern or metal silicide layer pattern **230** also diffuses to a region adjacent to the region **220a**.

[0058] Consequently, referring to FIG. 3E, most of the crystallization-inducing metals in the polycrystalline silicon layer **220** diffuse to the region **220a** corresponding to the metal layer pattern or metal silicide layer pattern **230** to be gettered over time, and thus only a few crystallization-inducing metals remain outside the region **220a**. According to this principle, the crystallization-inducing metal remaining in a

region to be a channel in the polycrystalline silicon layer **220** may be removed using the metal layer pattern or metal silicide layer pattern **230**.

[0059] FIG. 4 is a cross-sectional view illustrating a process of fabricating a polycrystalline silicon layer using a method of fabricating the polycrystalline silicon layer according to a second embodiment of the present invention. Except for particular descriptions in the second embodiment that differ from the first embodiment, the process will be described with reference to the descriptions in the first embodiment.

[0060] First, a substrate **400** having a buffer layer **410** is provided. Then, a metal layer pattern or metal silicide layer pattern **420** is formed in a predetermined region on the buffer layer **410** to correspond to a region that does not include where a channel region will be formed later.

[0061] Subsequently, an amorphous silicon layer is formed on the substrate **400** having the metal layer pattern or metal silicide layer pattern **420**, and crystallized into a polycrystalline silicon layer **430** using crystallization-inducing metal as described in the embodiment of FIGS. 1A through 1D. Here, during annealing for crystallization, a gettering process in which the crystallization-inducing metal moves to a region **430a** in the polycrystalline silicon layer **430** corresponding to the metal layer pattern or metal silicide layer pattern **420** may be simultaneously performed.

[0062] Then, the substrate **400** having the buffer layer **410**, the metal layer pattern or metal silicide layer pattern **420** and the polycrystalline silicon layer **430** is annealed. The annealing process allows the crystallization-inducing metal existing in the region that will form a channel in the polycrystalline silicon layer **430** to diffuse to the region **430a** in the polycrystalline silicon layer **430** corresponding to the metal layer pattern or metal silicide layer pattern **420** so as to getter the crystallization-inducing metal in the channel region of the polycrystalline silicon layer **430**.

[0063] FIGS. 5A to 5C are cross-sectional views illustrating a process of fabricating a top-gate thin film transistor (TFT) including fabricating a polycrystalline silicon layer according to the first embodiment of the present invention.

[0064] Referring to FIG. 5A, a buffer layer **510** may be formed of silicon oxide, silicon nitride or a combination thereof on a substrate **500**, which is formed of glass, stainless steel or plastic. The buffer layer **510** serves to prevent the diffusion of moisture or impurities generated on the substrate **500** and/or adjusts a heat transfer rate in crystallization so the amorphous silicon layer is crystallized easily.

[0065] Subsequently, an amorphous silicon layer is formed on the buffer layer **510**, and crystallized into a polycrystalline silicon layer using crystallization-inducing metal as in the embodiment of FIGS. 1A through 1D. The polycrystalline silicon layer is patterned to form a semiconductor layer **520**. Alternatively, the patterning process of polycrystalline silicon layer may be performed in a subsequent process.

[0066] Then, a metal layer pattern or metal silicide layer pattern **530** is formed on the semiconductor layer **520** to be in contact with a top surface of a region excluding the region that will become a channel controlling the current of a TFT.

[0067] The metal layer pattern or metal silicide layer pattern **530** may be formed on the semiconductor layer **520** to be spaced 50  $\mu\text{m}$  or less apart from the region to be a channel in the semiconductor layer **520**. When the metal layer pattern or metal silicide layer pattern **530** is formed in a region spaced more than 50  $\mu\text{m}$  apart from the channel region, the crystallization-inducing metal existing in the channel region has to

diffuse farther to be gettered in this region. In this case, due to a longer annealing needed to diffuse the crystallization-inducing metal over a longer distance, the substrate may be transformed, and thus the crystallization-inducing metal may be difficult to diffuse to this region.

[0068] Then, referring to FIG. 5B, the metal layer pattern or metal silicide layer pattern 530 may be formed to a thickness of 30 to 10000 Å. When the thickness is less than 30 Å, the crystallization-inducing metal may not be effectively gettered in the region of the semiconductor layer 520 corresponding to the metal layer pattern or metal silicide layer pattern 530. However, when the thickness is more than 10000 Å, the metal layer pattern or metal silicide layer pattern 530 becomes thick, and thus peeling of the layers may occur due to stress.

[0069] Then, the substrate 500 having the buffer layer 510, the semiconductor layer 520 and the metal layer pattern or metal silicide layer pattern 530 is annealed, thereby diffusing the crystallization-inducing metal remaining in the channel region of the semiconductor layer 520 to a region 520a in the semiconductor layer 520 corresponding to the metal layer pattern or metal silicide layer pattern 530 to be gettered. The annealing process is the same as that described in the method of fabricating the polycrystalline silicon layer, and may be performed at any time after forming the metal layer pattern or metal silicide layer pattern 530. As a result of the annealing process, the concentration of the crystallization-inducing metal remaining in the channel region of the semiconductor layer 520 is reduced to under  $10^{13}$  atoms/cm<sup>2</sup>. After annealing, the metal layer pattern or metal silicide layer pattern 530 may be removed.

[0070] Meanwhile, in order to improve gettering effect, an n-type impurity or a p-type impurity may be further implanted into a region 520a in the semiconductor layer 520 corresponding to the metal layer pattern or metal silicide layer pattern 530. As non-limiting examples, the n-type impurity may be phosphorus (P), and the p-type impurity may be boron (B). Also, a damage region 520b may be formed using ions or plasma in the region 520a in the semiconductor layer 520 corresponding to the metal layer pattern or metal silicide layer pattern 530 so as to improve the gettering effect.

[0071] Then, referring to FIG. 5C, a gate insulating layer 540 is formed on the semiconductor layer 520 having the metal layer pattern or metal silicide layer pattern 530. As non-limiting examples, the gate insulating layer 540 may be formed of silicon oxide, silicon nitride or a combination thereof.

[0072] Subsequently, a metal layer for a gate electrode (not illustrated) is formed on the gate insulating layer 540 using a single layer of Al or an Al alloy such as Al—Nd, or a multi-layer having an Al alloy on a Cr or Mo alloy, and a gate electrode 550 is formed to correspond to a channel region of the semiconductor layer 520 by etching the metal layer for a gate electrode using a photolithography process.

[0073] Then, an interlayer insulating layer 560 is formed on the entire surface of the substrate having the gate electrode 550. As non-limiting examples, the interlayer insulating layer 560 may be formed of silicon oxide, silicon nitride or a combination thereof.

[0074] After that, the interlayer insulating layer 560 and the gate insulating layer 540 are etched to form contact holes exposing source and drain regions of the semiconductor layer 520. Source and drain electrodes 571 and 572 connected to the source and drain regions through the contact holes are formed. As non-limiting examples, the source and drain elec-

trodes 571 and 572 may be formed of a material selected from the group consisting of Mo, Cr, W, MoW, Al, Al—Nd, Ti, TiN, Cu, a Mo alloy, an Al alloy and a Cu alloy. Thus, a TFT having the semiconductor layer 520, the gate electrode 550 and the source and drain electrodes 571 and 572 is completed.

[0075] FIGS. 6A to 6C are cross-sectional views illustrating a process of fabricating a bottom-gate TFT using the method of fabricating a polycrystalline silicon layer according to the first embodiment of the present invention. Except particular descriptions below, the process will be described with reference to the descriptions in the above embodiment.

[0076] Referring to FIG. 6A, a buffer layer 610 is formed on a substrate 600. A metal layer for a gate electrode (not illustrated) is formed on the buffer layer 610, and a gate electrode 620 is formed by etching the metal layer for a gate electrode using a photolithography process. Then, a gate insulating layer 630 is formed on the substrate 600 having the gate electrode 620.

[0077] Subsequently, referring to FIG. 6B, an amorphous silicon layer is formed on the gate insulating layer 630, and then crystallized into a polycrystalline silicon layer using crystallization-inducing metal as described in the embodiment of FIGS. 1A through 1D. The polycrystalline silicon layer is patterned to form a semiconductor layer 640. Alternatively, the patterning may be performed in a subsequent process.

[0078] Then, a metal layer pattern or metal silicide layer pattern 650 is formed on the top surface of the semiconductor layer 640 excluding a region that will be a channel controlling current in the TFT by the same method as that described in the method of fabricating a polycrystalline silicon layer according to the first embodiment of the present invention. Alternatively, the metal layer pattern or metal silicide layer pattern 650 may be formed on the gate insulating layer 630 before forming the amorphous silicon layer that forms the semiconductor layer 640.

[0079] Subsequently, the substrate 600 having the buffer layer 610, the gate electrode 620, the gate insulating layer 630, the semiconductor layer 640 and the metal layer pattern or metal silicide layer pattern 650 is annealed to diffuse the crystallization-inducing metal remaining in the channel region of the semiconductor layer 640 to a region 640a in the semiconductor layer 640 corresponding to the metal layer pattern or metal silicide layer pattern 650, so as to getter the crystallization-inducing metal. The annealing process is the same as described in the method of fabricating the polycrystalline silicon layer, and may be performed at any time after forming the metal layer pattern or metal silicide layer pattern 650. After the annealing process, the metal layer pattern or metal silicide layer pattern 650 may be removed.

[0080] Then, referring to FIG. 6C, an ohmic contact material layer and source and drain conductive layers are sequentially stacked on the semiconductor layer 640 having the metal layer pattern or metal silicide layer pattern 650, and patterned to form source and drain electrodes 671 and 672 and an ohmic contact layer 660. As a non-limiting example, the ohmic contact layer 660 may be an impurity-doped amorphous silicon layer.

[0081] The source and drain conductive layers and the ohmic contact material layer may be patterned using a single mask, thereby avoiding the extra time and expense of using a separate mask for each layer. Thus, the ohmic contact layer 660 may be disposed under the entire surface of the source and drain electrodes 671 and 672. The ohmic contact layer

**660** may be interposed between the semiconductor layer **640** and the source and drain electrodes **671** and **672** to ohmically contact the semiconductor layer **640** with the source and drain electrodes **671** and **672**. Alternatively, the ohmic contact layer **660** may be omitted. In this case, before stacking the source and drain conductive layers, a conductive region may be formed in the semiconductor layer **640** to be in ohmic contact with the source and drain electrodes **671** and **672**. Thus, a bottom gate TFT including the gate electrode **620**, the semiconductor layer **640** and the source and drain electrodes **671** and **672** is completed.

**[0082]** FIGS. 7A to 7C are cross-sectional views illustrating a process of fabricating a top-gate TFT using the method of fabricating a polycrystalline silicon layer according to the second embodiment of the present invention. Except for particular descriptions below, the process will be described with reference to the descriptions as in the above second embodiment.

**[0083]** First, referring to FIG. 7A, a substrate **700** having a buffer layer **710** is provided. Then, a metal layer pattern or metal silicide layer pattern **720** is formed in a predetermined region on the buffer layer **710** to correspond to a region that is outside a channel region in a semiconductor layer to be formed later.

**[0084]** Subsequently, referring to FIG. 7B, an amorphous silicon layer is formed on the substrate **700** having the metal layer pattern or metal silicide layer pattern **720**, and crystallized into a polycrystalline silicon layer using crystallization-inducing metal as described in the embodiment of FIGS. 1A to 1D. The polycrystalline silicon layer is patterned to form a semiconductor layer **730**. Alternatively, the patterning may be performed in a subsequent process.

**[0085]** Then, the substrate **700** having the buffer layer **710**, the metal layer pattern or metal silicide layer pattern **720** and the semiconductor layer **730** is annealed, thereby diffusing the crystallization-inducing metal remaining in a channel region of the semiconductor layer **730** to a region **730a** in the semiconductor layer **730** corresponding to the metal layer pattern or metal silicide layer pattern **720** so as to getter the crystallization-inducing metal in the channel region of the semiconductor layer **730**. The annealing process may be performed at any time after forming the metal layer pattern or metal silicide layer pattern **720**.

**[0086]** Subsequently, referring to FIG. 7C, a gate insulating layer **740** is formed on the semiconductor layer **730**. Then, a metal layer for a gate electrode (not illustrated) is formed, and a gate electrode **750** is formed to correspond to the channel region of the semiconductor layer **730** by etching the metal layer for a gate electrode using a photolithography process.

**[0087]** After that, an interlayer insulating layer **760** is formed on the entire surface of the substrate having the gate electrode **750**, and the interlayer insulating layer **760** and the gate insulating layer **740** are etched to form contact holes exposing source and drain regions of the semiconductor layer **730**. Source and drain electrodes **771** and **772** connected to the source and drain regions through the contact holes are formed. Thus, a TFT having the semiconductor layer **730**, the gate electrode **750** and the source and drain electrodes **771** and **772** is completed.

**[0088]** While, in the present embodiment, the top-gate TFT having a gate electrode formed on a gate insulating layer is described, it may be understood to those of ordinary skill in the art that the present invention may be modified and trans-

formed in various ways, for example, in application to a bottom-gate TFT, without departing from the scope of the present invention.

**[0089]** FIG. 8 is a comparison graph of off-currents per unit width (A/μm) between a semiconductor layer of a TFT formed by a conventional gettering method through phosphorus (P) doping and a semiconductor layer of a TFT formed by a method of fabricating a polycrystalline silicon layer according to aspects of the present invention. Here, section A on a horizontal axis denotes a TFT using the conventional gettering method by P-doping, and sections B and C denote a TFT using the method of fabricating a polycrystalline silicon layer according to the present invention, wherein in section B, Ti was used in the metal layer pattern, and in section C, Mo was used in the metal layer pattern. The vertical axis denotes an off-current per unit width (A/μm) of a semiconductor layer in a TFT.

**[0090]** The conventional gettering method by P-doping was performed by doping phosphorus into a region excluding the channel of a semiconductor layer at a dose of  $2 \times 10^{14} \text{ cm}^{-2}$ , and annealing the semiconductor layer for an hour at 550°C. The method of fabricating a polycrystalline silicon layer according to aspects of the present invention was performed by depositing Ti or Mo to have a thickness of 100 Å on the region excluding the channel of a semiconductor layer, respectively, and annealing the semiconductor layer under the same conditions as those described in the gettering method by P-doping. After annealing, the off-currents per unit width of the semiconductor layer of each transistor were measured.

**[0091]** According to aspects of the present invention, when depositing Ti or Mo onto a region of a semiconductor layer and annealing the semiconductor layer for gettering, Ti or Mo reacts with Si of the semiconductor layer to form Ti silicide or Mo silicide. In a lower region of the semiconductor layer in contact with the Ti or Mo layer, a region is formed in which Ti silicide or Mo silicide is grown from an interface of the semiconductor layer, and crystallization-inducing metal is gettered therein.

**[0092]** Referring to section A of FIG. 8, the off-current per unit width of the semiconductor layer of the TFT using the conventional gettering method by P-doping was approximately  $4.5 \times 10^{-12}$  to  $7.0 \times 10^{-12}$  (A/μm). In contrast, referring to sections B and C of FIG. 8, the off-current per unit width of the semiconductor layer of the TFT by the method of fabricating a polycrystalline silicon layer according to aspects of the present invention using Ti was  $5.0 \times 10^{-13}$  (A/μm) or less, and that using Mo was  $6.0 \times 10^{-13}$  (A/μm) or less. Thus, it may be seen that the off-current per unit width was significantly lowered in a TFT according to aspects of the present invention in comparison to a TFT formed according to the conventional method.

**[0093]** Consequently, by using the method of fabricating a polycrystalline silicon layer according to aspects of the present invention, it may be seen that the amount of crystallization-inducing metal remaining in the channel region of the semiconductor layer, which affects an off-current of a TFT, drastically decreases, and thus a TFT having a significantly low leakage current and an excellent electrical characteristic may be provided.

**[0094]** FIG. 9 is a cross-sectional view of an organic light emitting diode (OLED) display device including a TFT according to an embodiment of the present invention.

**[0095]** Referring to FIG. 9, an insulating layer **575** is formed on the entire surface of the substrate **500** including the

TFT according to the embodiment of FIG. 5C. The insulating layer 575 may be an inorganic layer formed of a material selected from the group consisting of silicon oxide, silicon nitride and silicate on glass, or an organic layer formed of a material selected from the group consisting of polyimide, benzocyclobutene series resin and acrylate. Also, the insulating layer may be formed by stacking the inorganic layer and the organic layer.

[0096] A via hole exposing the source or drain electrode 571 or 572 is formed by etching the insulating layer 575. A first electrode 580 connected to one of the source and drain electrodes 571 and 572 through the via hole is formed. The first electrode 580 may be an anode or a cathode. When the first electrode 580 is an anode, the anode may be formed of a transparent conductive layer formed of ITO, IZO or ITZO, and when the first electrode 580 is a cathode, the cathode may be formed of Mg, Ca, Al, Ag, Ba or an alloy thereof.

[0097] Then, a pixel defining layer 585 having an opening that partially exposes the surface of the first electrode 580 is formed on the first electrode 580, and an organic layer 590 including an emission layer is formed on the exposed first electrode 580. The organic layer 590 may further include at least one of a hole injection layer, a hole transport layer, a hole blocking layer, an electron blocking layer, an electron injection layer and an electron transport layer. Then, a second electrode 595 is formed on the organic layer 590. Thus, an OLED display device according to the embodiment of the present invention is completed.

[0098] In summary, in a polycrystalline silicon layer crystallized using crystallization-inducing metal, a metal layer pattern or metal silicide layer pattern including a metal or an alloy thereof having a smaller diffusion coefficient than the crystallization-inducing metal in the polycrystalline silicon layer may be formed over or under a predetermined region corresponding to a region that a channel in the polycrystalline silicon layer and then the polycrystalline silicon layer may be annealed, thereby removing the crystallization-inducing metal existing in the channel region of the polycrystalline silicon layer. As a result, an off-current of a TFT containing the semiconductor layer may be significantly reduced, and a TFT having an excellent electrical characteristics and an OLED display device including the same may be provided.

[0099] According to aspects of the present invention as described above, crystallization-inducing metal existing in a channel region of a polycrystalline silicon layer may be completely removed, and the region of the polycrystalline silicon layer from which the crystallization-inducing metal is completely removed may be used as a channel region of a TFT, and thus a TFT having an excellent electrical characteristic such as a low off-current, a method of fabricating the same, and an OLED display device including the TFT may be provided.

[0100] Although a few embodiments of the present invention have been shown and described, it would be appreciated by those skilled in the art that changes may be made in this embodiment without departing from the principles and spirit of the invention, the scope of which is defined in the claims and their equivalents.

What is claimed is:

1. A method of removing a crystallization-inducing metal from a first predetermined region of a polycrystalline silicon layer crystallized using a crystallization-inducing metal, the method comprising:

providing a metal layer pattern or metal silicide layer pattern in contact with the polycrystalline silicon layer in a second predetermined region of the polycrystalline silicon layer; and

performing annealing to getter the crystallization-inducing metal existing in the first predetermined region to the second predetermined region.

2. The method of claim 1, wherein the providing of the metal layer pattern or metal silicide layer pattern in contact with the polycrystalline silicon layer in a second predetermined region of the polycrystalline silicon layer is carried out by forming the metal layer pattern or metal silicide layer pattern on the polycrystalline silicon layer in the second predetermined region of the polycrystalline silicon layer.

3. The method of claim 1, wherein the providing of the metal layer pattern or metal silicide layer pattern in contact with the polycrystalline silicon layer in a second predetermined region of the polycrystalline silicon layer is carried out by forming the metal layer pattern or metal silicide layer pattern on a substrate, forming an amorphous silicon layer such that a first region of the amorphous silicon layer that becomes the first predetermined region contacts the substrate and a second region of the amorphous silicon layer that becomes the second predetermined region contacts the metal layer pattern or metal silicide layer pattern and crystallizing the amorphous silicon layer using a crystallization-inducing metal to form the polycrystalline silicon layer.

4. The method of claim 1, wherein the second predetermined region is formed at a distance of 50  $\mu\text{m}$  or less from the first predetermined region.

5. The method according to claim 1, wherein the metal or metal silicide included in the metal layer pattern or metal silicide layer pattern has a smaller diffusion coefficient than the diffusion coefficient of the crystallization-inducing metal in the polycrystalline silicon layer.

6. The method according to claim 5, wherein the metal or metal silicide included in the metal layer pattern or metal silicide layer pattern has a diffusion coefficient of  $1/100$  or less of the diffusion coefficient of the crystallization-inducing metal.

7. The method according to claim 6, wherein the crystallization-inducing metal comprises nickel, and the diffusion coefficient of the metal or metal silicide included in the metal layer pattern or metal silicide layer pattern is from more than 0 to  $10^{-7} \text{ cm}^2/\text{s}$ .

8. The method according to claim 6, wherein the metal layer pattern or metal silicide layer pattern comprises one selected from the group consisting of scandium (Sc), titanium (Ti), zirconium (Zr), hafnium (Hf), vanadium (V), niobium (Nb), tantalum (Ta), chromium (Cr), molybdenum (Mo), tungsten (W), manganese (Mn), rhenium (Re), ruthenium (Ru), osmium (Os), cobalt (Co), rhodium (Rh), iridium (Ir), platinum (Pt), yttrium (Y), lanthanum (La), cerium (Ce), praseodymium (Pr), neodymium (Nd), dysprosium (Dy), holmium (Ho), titanium nitride (TiN), tantalum nitride (Ta<sub>N</sub>) and an alloy or silicide thereof.

9. The method according to claim 1, wherein the annealing is performed for 10 seconds to 10 hours at a temperature of 500 to 993° C.

10. The method of claim 1, wherein the metal layer pattern or metal silicide layer pattern when formed does not include any metal or metal silicide having a diffusion coefficient greater than  $10^{-7} \text{ cm}^2/\text{s}$ .

**11.** The method according to claim 1, wherein the polycrystalline silicon layer crystallized using a crystallization-inducing metal is formed by a metal-induced crystallization (MIC) technique, a metal-induced lateral crystallization (MILC) technique or a super grain silicon (SGS) technique.

**12.** The method according to claim 1, wherein the metal layer pattern or metal silicide layer pattern is formed to a thickness of 30 to 10000 Å.

**13.** The method according to claim 12, wherein the metal layer pattern or metal silicide layer pattern is formed to a thickness of 30 to 2000 Å.

**14.** The method according to claim 1, further comprising: implanting an n-type impurity or a p-type impurity into the region of the polycrystalline silicon layer corresponding to the metal layer pattern or metal silicide layer pattern, or forming a damage region in the region of the semiconductor layer corresponding to the metal layer pattern or metal silicide layer pattern using ions or plasma.

**15.** The method according to claim 1, wherein the first predetermined region is a channel region in the polycrystalline silicon layer.

**16.** A thin film transistor, comprising:

a substrate;

a semiconductor layer disposed on the substrate and including a channel region, and source and drain regions;

a metal layer pattern or metal silicide layer pattern disposed over or under the semiconductor layer corresponding to a region excluding the channel region;

a gate electrode disposed to correspond to the channel region of the semiconductor layer;

a gate insulating layer interposed between the gate electrode and the semiconductor layer to insulate the semiconductor layer from the gate electrode; and

source and drain electrodes electrically connected to the source and drain regions of the semiconductor layer.

**17.** The thin film transistor according to claim 16, wherein the metal layer pattern or metal silicide layer pattern includes a metal or metal silicide having a smaller diffusion coefficient in the semiconductor layer than the crystallization-inducing metal or an alloy thereof.

**18.** The thin film transistor according to claim 17, wherein the metal or metal silicide included in the metal layer pattern or metal silicide layer pattern has a diffusion coefficient of  $1/100$  or less of that of the crystallization-inducing.

**19.** The thin film transistor according to claim 18, wherein the crystallization-inducing metal comprises nickel, and the diffusion coefficient of the metal or metal silicide included in the metal layer pattern or metal silicide layer pattern is from more than 0 to  $10^{-7}$  cm<sup>2</sup>/s.

**20.** The thin film transistor according to claim 17, wherein the metal layer pattern or metal silicide layer pattern comprises one selected from the group consisting of Sc, Ti, Zr, Hf, V, Nb, Ta, Cr, Mo, W, Mn, Re, Ru, Os, Co, Rh, Ir, Pt, Y, La, Ce, Pr, Nd, Dy, Ho, TiN, TaN and an alloy or silicide thereof.

**21.** The thin film transistor according to claim 16, wherein the metal layer pattern or metal silicide layer pattern is spaced 50 µm or less apart from the channel region of the semiconductor layer.

**22.** The thin film transistor according to claim 16, wherein the metal layer pattern or metal silicide layer pattern has a thickness of 30 to 10000 Å.

**23.** The thin film transistor according to claim 16, further comprising:

an n-type impurity or a p-type impurity in a predetermined region of the semiconductor layer corresponding to the metal layer pattern or metal silicide layer pattern, or a damage region formed in the predetermined region of the semiconductor layer corresponding to the metal layer pattern or metal silicide layer pattern using ions or plasma.

**24.** The thin film transistor according to claim 16, wherein a concentration of a crystallization-inducing metal in the channel region of the semiconductor layer is less than  $10^{13}$  atmos/cm<sup>2</sup>.

**25.** A method of fabricating a thin film transistor, comprising:

preparing a substrate;

forming an amorphous silicon layer on the substrate;

crystallizing the amorphous silicon layer into a polycrystalline silicon layer using crystallization-inducing metal;

forming a metal layer pattern or metal silicide layer pattern in contact with an upper or lower region of the polycrystalline silicon layer corresponding to a region excluding a channel region in the polycrystalline silicon layer;

forming a gate electrode corresponding to the channel region of the polycrystalline silicon layer;

forming a gate insulating layer between the gate electrode and the polycrystalline silicon layer to insulate the polycrystalline silicon layer from the gate electrode;

forming source and drain electrodes electrically connected to source and drain regions of the polycrystalline silicon layer; and

after forming the metal layer pattern or metal silicide layer pattern, annealing the substrate to getter the crystallization-inducing metal existing in the channel region of the polycrystalline silicon layer to a region of the polycrystalline silicon layer corresponding to the metal layer pattern or metal silicide layer pattern.

**26.** The method according to claim 25, further comprising:

after annealing the substrate to getter the crystallization-inducing metal existing in the channel region of the polycrystalline silicon layer, removing the metal layer pattern or metal silicide layer pattern.

**27.** The method according to claim 25, wherein the metal layer pattern or metal silicide layer pattern includes a metal or metal silicide having a smaller diffusion coefficient in the polycrystalline silicon layer than that of the crystallization-inducing metal or an alloy thereof.

**28.** The method according to claim 27, wherein the metal or metal silicide of the metal layer pattern or metal silicide layer pattern has a diffusion coefficient of  $1/100$  or less of that of the crystallization-inducing metal.

**29.** The method according to claim 28, wherein the crystallization-inducing metal comprises nickel, and the diffusion coefficient of the metal or metal silicide of the metal layer pattern or metal silicide layer pattern is more than 0 to  $10^{-7}$  cm<sup>2</sup>/s or less.

**30.** The method according to claim 28, wherein the metal layer pattern or metal silicide layer pattern comprises one selected from the group consisting of Sc, Ti, Zr, Hf, V, Nb, Ta, Cr, Mo, W, Mn, Re, Ru, Os, Co, Rh, Ir, Pt, Y, La, Ce, Pr, Nd, Dy, Ho, TiN, TaN and an alloy or silicide thereof.

**31.** The method according to claim 25, wherein the annealing is performed for 10 seconds to 10 hours at a temperature of 500 to 993°C.

**32.** The method according to claim 25, wherein the crystallizing of the amorphous silicon layer is performed by an MIC, MILC or SGS technique.

**33.** The method according to claim 25, further comprising: implanting an n-type impurity or a p-type impurity into the region of the polycrystalline silicon layer corresponding to the metal layer pattern or metal silicide layer pattern, or forming a damage region in the region of the polycrystalline silicon layer corresponding to the metal layer pattern or metal silicide layer pattern using ions or plasma.

**34.** An organic light emitting diode (OLED) display device, comprising:

a substrate;

a semiconductor layer disposed on the substrate, and including a channel region and source and drain regions;

a metal layer pattern or metal silicide layer pattern disposed over or under the semiconductor layer corresponding to a region excluding the channel region;

a gate electrode disposed to correspond to the channel region of the semiconductor layer;

a gate insulating layer interposed between the gate electrode and the semiconductor layer to insulate the semiconductor layer from the gate electrode;

source and drain electrodes electrically connected to the source and drain regions of the semiconductor layer;

a first electrode electrically connected to one of the source and drain electrodes;

an organic layer disposed on the first electrode; and

a second electrode disposed on the organic layer.

**35.** The OLED display device according to claim 34, wherein the metal layer pattern or metal silicide layer pattern includes a metal or metal silicide having a smaller diffusion

coefficient in the semiconductor layer than the crystallization-inducing metal or an alloy thereof.

**36.** The OLED display device according to claim 34, wherein the metal or metal silicide of the metal layer pattern or metal silicide layer pattern has a diffusion coefficient of  $\frac{1}{100}$  or less of that of the crystallization-inducing metal.

**37.** The OLED display device according to claim 36, wherein the crystallization-inducing metal comprises nickel, and the diffusion coefficient of the metal layer pattern or metal silicide layer pattern is from more than 0 to  $10^{-7} \text{ cm}^2/\text{s}$ .

**38.** The OLED display device according to claim 36, wherein the metal layer pattern or metal silicide layer pattern comprises one selected from the group consisting of Sc, Ti, Zr, Hf, V, Nb, Ta, Cr, Mo, W, Mn, Re, Ru, Os, Co, Rh, Ir, Pt, Y, La, Ce, Pr, Nd, Dy, Ho, TiN, TaN and an alloy thereof, or silicide thereof.

**39.** The OLED display device according to claim 34, wherein the metal layer pattern or metal silicide layer pattern is spaced 50  $\mu\text{m}$  or less apart from the channel region of the semiconductor layer.

**40.** The OLED display device according to claim 34, wherein the metal layer pattern or metal silicide layer pattern has a thickness of 30 to 10000 Å.

**41.** The OLED display device according to claim 34, further comprising:

an n-type impurity or a p-type impurity in the semiconductor layer corresponding to the metal layer pattern or metal silicide layer pattern, or a damage region formed in the semiconductor layer corresponding to the metal layer pattern or metal silicide layer pattern using ions or plasma.

**42.** The OLED display device according to claim 34, wherein the channel region of the semiconductor layer is devoid of a crystallization-inducing metal.

\* \* \* \* \*

|               |                                                                                                       |         |            |

|---------------|-------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)       | 制造多晶硅层的方法，使用其制造的TFT，制造TFT的方法以及具有该方法的有机发光二极管显示装置                                                       |         |            |

| 公开(公告)号       | <a href="#">US20080296565A1</a>                                                                       | 公开(公告)日 | 2008-12-04 |

| 申请号           | US12/130340                                                                                           | 申请日     | 2008-05-30 |

| 申请(专利权)人(译)   | 三星SDI CO. , LTD.                                                                                      |         |            |

| 当前申请(专利权)人(译) | 三星移动显示器有限公司.                                                                                          |         |            |

| [标]发明人        | PARK BYOUNG KEON<br>SEO JIN WOOK<br>YANG TAE HOON<br>LEE KIL WON<br>LEE KI YONG                       |         |            |

| 发明人           | PARK, BYOUNG-KEON<br>SEO, JIN-WOOK<br>YANG, TAE-HOON<br>LEE, KIL-WON<br>LEE, KI-YONG                  |         |            |

| IPC分类号        | H01L51/52 H01L21/322 H01L29/786 H01L21/336                                                            |         |            |

| CPC分类号        | H01L21/02488 H01L21/02532 H01L21/02672 H01L27/1277 H01L29/66757 H01L29/66765 H01L29/78618 H01L21/3221 |         |            |

| 优先权           | 1020070053314 2007-05-31 KR                                                                           |         |            |

| 外部链接          | <a href="#">Espacenet</a> <a href="#">USPTO</a>                                                       |         |            |

## 摘要(译)

一种制造多晶硅层的方法，包括：在衬底上形成非晶硅层；使用结晶诱导金属将非晶硅层结晶成多晶硅层；形成与多晶硅层的上部或下部区域接触的金属层图案或金属硅化物层图案，所述多晶硅层的上部或下部区域对应于除多晶硅层中的沟道区域之外的区域；对基板进行退火，以使存在于多晶硅层的沟道区域中的结晶诱导金属吸收到具有金属层图案或金属硅化物层图案的多晶硅层中的区域。因此，可以有效地去除存在于多晶硅层的沟道区中的结晶诱导金属，因此可以制造具有改善的漏电流特性的薄膜晶体管和包括该晶体管的OLED显示装置。